ECL (emitter coupled logic) ble først oppfunnet hos IBM i august 1956 av Hannon S. Yourke. Denne logikken er også kjent som strømmoduslogikk, brukt i datamaskinene til IBM 7090 og 7094. ECL-familien er veldig rask sammenlignet med digital logikk familier. Generelt gir denne logikkfamilien en forplantningsforsinkelse på mindre enn 1 ns. Det er en logikkfamilie basert på bipolare koblingstransistorer. Det er den raskeste logiske familiekretsen som er tilgjengelig for å designe et konvensjonelt logikksystem. Denne artikkelen diskuterer en oversikt over en emitterkoblet logikk-krets , jobber med applikasjoner.

Hva er emitterkoblet logikk?

Emitter-koblet logikk er den beste BJT -basert logikkfamilie brukt i konvensjonell logikksystemdesign. Noen ganger kalles det også gjeldende moduslogikk, som er en svært høyhastighets digital teknologi. Generelt regnes ECL som den raskeste logiske IC der den oppnår sin høyhastighetsdrift ved å bruke en veldig liten spenningssving og også unngå at transistorene kommer inn i metningsområdet.

En implementering av ECL bruker en positiv forsyningsspenning som er kjent som PECL eller positiv-referert ECL. I tidlige ECL-porter brukes en negativ spenningsforsyning på grunn av støyimmuniteten. Etter det ble positivt referert ECL veldig kjent på grunn av dets mer kompatible logikknivåer sammenlignet med TTL-logikkfamilier.

Emitterkoblet logikk sprer en enorm mengde statisk kraft, men dets totale strømforbruk er lavt sammenlignet med CMOS ved høye frekvenser. Så ECL er hovedsakelig fordelaktig i klokkedistribusjonskretser og høyfrekvensbaserte applikasjoner.

Emitterkoblede logiske funksjoner

Funksjonene til ECL vil gjøre dem brukt i mange høyytelsesbaserte applikasjoner.

- ECL gir to utganger som alltid komplementerer hverandre fordi driften av kretsen er basert på en differensialforsterker.

- Denne logikkfamilien er hovedsakelig egnet for monolittiske fremstillingsmetoder fordi logiske nivåer er en funksjon av motstandsforhold.

- Enhetene i ECL-familien genererer den riktige og komplementære utgangen til den foreslåtte funksjonen uten bruk av eksterne omformere. Følgelig reduserer det pakkeantallet og kraftbehovet og reduserer også problemer som oppstår på grunn av tidsforsinkelser.

- ECL-enheter i differensialforsterkerdesign tilbyr bred ytelsesfleksibilitet, så ECL-kretser gjør det mulig å bruke både som digitale og lineære kretser.

- Utformingen av ECL-porten har normalt høy og lav inngangsimpedans, noe som er ekstremt gunstig for å oppnå stor fan-out samt kjørekapasitet.

- ECL-enheter genererer et konstant strømforbruk på strømforsyningen for å forenkle utformingen av strømforsyningen.

- Enhetene til ECL inkludert åpne emitterutganger lar dem ganske enkelt inkludere overføringslinjedriftkapasitet.

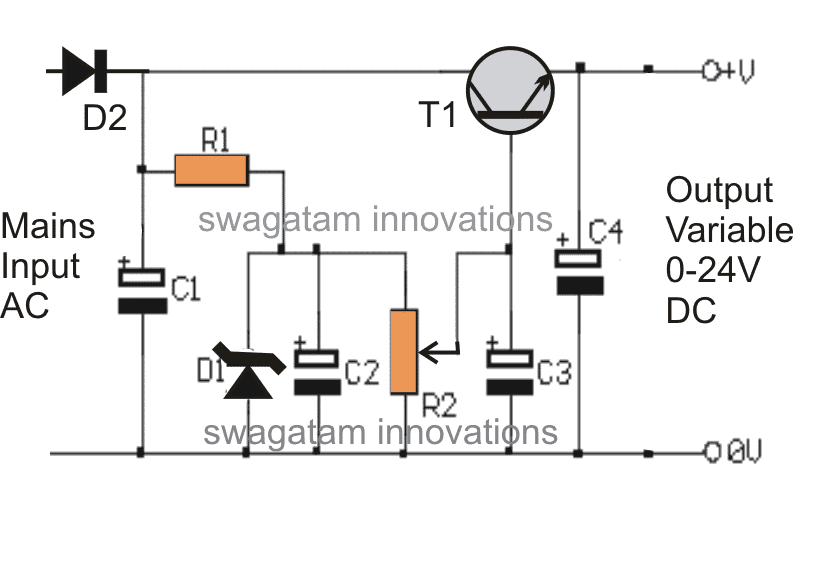

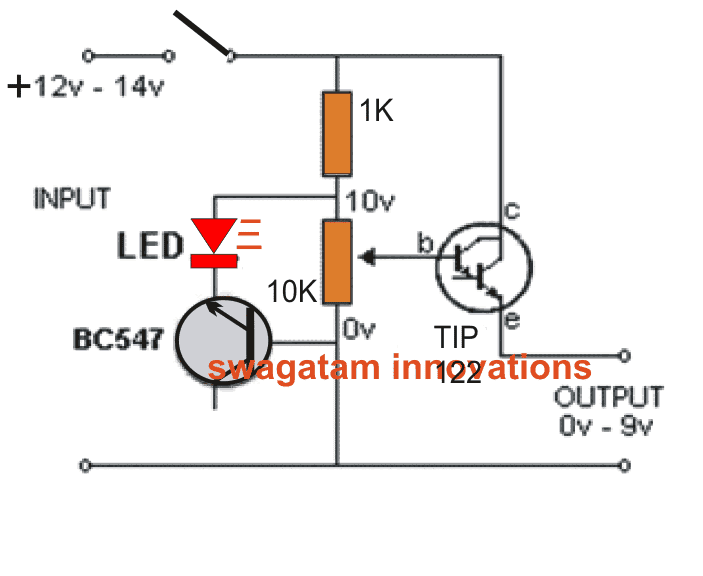

Emitterkoblet logisk krets

Den emitterkoblede logiske kretsen for omformeren er vist nedenfor som er designet med motstander og transistorer. I denne kretsen er emitterterminalene til to transistorer ganske enkelt koblet til strømbegrensende motstand RE som brukes for å unngå at transistoren går inn i metning. Her tas transistorens utgang fra kollektorterminalen i stedet for emitterterminalen. Denne kretsen gir to utganger Vout (inverterende utgang) og Vout2 (ikke-inverterende utgang) og inngangsterminalen som Vin hvor høy eller lav inngang er gitt. +Vcc = 5V.

Hvordan fungerer emitterkoblet logikk?

Operasjonen til emitterkoblet logikk er at når HØY-inngangen er gitt til ECL-kretsen, vil den gjøre 'Q1'-transistoren PÅ og Q2-transistoren AV, men Q1-transistoren er ikke mettet. Så dette vil trekke VOUT2-utgangen til HØY og verdien av VOUT1-utgangen vil være LAV på grunn av fallet innenfor R1.

På samme måte, når VIN-verdien gitt til ECL er LAV, vil det gjøre Q1-transistoren AV og Q2-transistoren PÅ. Så Q2-transistoren vil ikke gå inn i metning. Så det vil gjøre at VOUT1-utgangen trekkes HØY verdi og VOUT2-utgangsverdien vil være lav på grunn av fallet innenfor R2-motstanden.

La se hvordan transistoren Q1 og Q2 slår seg på og av når en spenning påføres.

De to transistorene som Q1 og Q2 i denne kretsen er koblet som en differensialforsterker med en felles emittermotstand.

Spenningsforsyningen for denne eksempelkretsen er VCC = 5,0, VBB = 4,0 & VEE = 0 V. Inngangsverdiene HØYT & LAVT nivå er ganske enkelt definert til å være 4,4 V & 3,6V. Faktisk genererer denne kretsen LAV utgang og HØYE nivåer som er 0,6 volt høyere; dette er imidlertid korrigert innenfor ekte ECL-kretser.

Når Vin er HØY, er Q1-transistoren slått på, men ikke mettet og Q2-transistoren er slått av. Så utgangsspenning som VOUT2 trekkes til 5 V gjennom R2-motstanden, og det kan vises at spenningsfallet over R1-motstanden er omtrent 0,8 V slik at VOUT1 = 4,2 V (LAV). I tillegg VE = VOUT1 – VQ1 => 4,2V – 0,4V = 3,8V ettersom transistor Q1 er slått PÅ fullstendig.

Når Vin er LAV, vil Q2-transistoren være slått på, men ikke mettet og Q1-transistoren er slått AV. Derfor trekkes VOUT1 til 5,0 V ved hjelp av en R1-motstand og det kan vises at VOUT2 er 4,2 V. Også VE => VOUT2 – VQ2 => 4,2V – 0,8V => 3,4V når transistor Q2 er slått PÅ.

I ECL er de to transistorene aldri i metning som t svingningene i inngangs-/utgangsspenningen er ganske små som 0,8V og inngangsimpedansen er høy og utgangsmotstanden er lav. Dette hjelper ECL med å fungere raskere med en mindre forsinkelsestid.

To inngangs emitter koblet logisk ELLER/NOR portkrets

Den logiske ELLER/NOR-portkretsen med to inngangs-emitterkoblede er vist nedenfor. Denne kretsen er designet ved å modifisere vekselretterkretsen ovenfor. Modifikasjonen er ved å legge til en ekstra transistor på inngangssiden.

Arbeidet med denne kretsen er veldig enkel. Når inngangene på både Q1 og Q2 transistorene er lave, vil utgangen1 (Vout1) få en HØY verdi. Så denne Vout1 tilsvarer utgangen fra NOR-porten.

Samtidig, hvis Q3-transistoren er slått PÅ, vil den få den andre utgangen (Vout2) til å være HØY. Så denne Vou2-utgangen tilsvarer OR-portutgangen.

På samme måte, hvis både Q1 & Q2 transistorinngangene er HØY, vil den slå på Q1 & Q2 transistorene og gi den lave utgangen på VOUT1 terminalen.

Hvis Q3-transistoren er slått AV under denne operasjonen, vil den gi høy utgang ved VOUT2-terminalen. Så, sannhetstabellen for OR/NOR-port er gitt nedenfor.

|

Innganger |

Innganger | ELLER |

HELLER IKKE |

|

EN |

B | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Emitter-koblede logiske egenskaper

Egenskapene til ECL inkluderer følgende.

- Sammenlignet med TTL har ECL en raskere forplantningstid fra 0,5 til 2 ns. Men emitterkoblet logisk effekttap er høyere sammenlignet med TTL som 30 mW.

- I/O-spenningene til ECL har en liten svingning som 0,8.

- Inngangsimpedansen til ECL er høy og utgangsmotstanden er lav; følgelig endrer transistoren sine tilstander veldig raskt.

- ECLs viftekapasitet er høy og gateforsinkelser er lave.

- O/p-logikken til ECL endres fra en LAV til en HØY tilstand, men spenningsnivåene for disse tilstandene vil variere mellom TTL og EC.

- Støyimmuniteten til ECL er 0,4V.

Fordeler og ulemper

De fordelene med emitterkoblet logikk er omtalt nedenfor.

- Fanout av ECL er 25 som er bedre sammenlignet med TTL og det er lavt sammenlignet med CMOS.

- Den gjennomsnittlige forplantningsforsinkelsen til ECL er 1 til 4 ns, noe som er bedre sammenlignet med både CMOS og

- TTL. Derfor kalles den raskeste logikkfamilie.

- Når BJT-ene i emitter koblet seg sammen logiske porter jobber i den aktive regionen, så har de maksimal hastighet sammenlignet med alle logikkfamilier.

- ECL-porter genererer komplementære utganger.

- Strømsvitsjetopper er ikke der i strømforsyningsledningene.

- Utganger kan kobles sammen for å gi kablet-ELLER-funksjonen.

- Parametrene til ECL endres ikke mye gjennom temperaturen.

- Nr. av funksjoner tilgjengelig fra en eneste brikke er høy.

De ulemper med emitterkoblet logikk er omtalt nedenfor.

- Den har en ekstremt mindre støymargin, dvs. ±200 mV.

- Effekttap er høyt sammenlignet med andre logiske porter.

- For å kommunisere med andre logikkfamilier er nivåskiftere nødvendig.

- Fanout begrenser kapasitiv belastning.

- Sammenlignet med TTL , ECL-porter er dyre.

- Sammenlignet med CMOS og TTL er ECL-støyimmunitet verst.

applikasjoner

Anvendelsene av emitterkoblet logikk inkluderer følgende.

- Emitterkoblet logikk brukes som en logikk- og grensesnittteknologi innenfor ekstremt høyhastighets kommunikasjonsenheter som fiberoptiske transceiver-grensesnitt, Ethernet og ATM-nettverk (Asynchronous Transfer Mode).

- ECL er en logikkfamilie basert på BJT der dens høyhastighetsdrift kan oppnås ved å bruke en relativt liten spenningssving og unngå at transistorene beveger seg inn i metningsområdet.

- ECL brukes til å lage ASLT-kretser i IBM 360/91.

- ECL unngår bruk av stablede transistorer ved å bruke en single-ended bias i/p og positiv tilbakemelding mellom primære og sekundære transistorer for å oppnå en inverterfunksjon.

- ECL brukes i ekstremt høyhastighets elektronikk.

Dermed er dette en oversikt over en emitterkoblet logikk eller ECL – krets, arbeid, funksjoner, egenskaper og applikasjoner. ECL er den aller raskeste logikkfamilien basert på BJT sammenlignet med andre digitale logikkfamilier. Den oppnår maksimal hastighet ved å bruke en liten spenningssving og unngå at transistorene beveger seg inn i metningsområdet. Denne logikkfamilien gir en utrolig 1ns forplantningsforsinkelse, og i de siste ECL-familiene er denne forsinkelsen redusert. Her er et spørsmål til deg, hva er et alternativt navn for ECL?