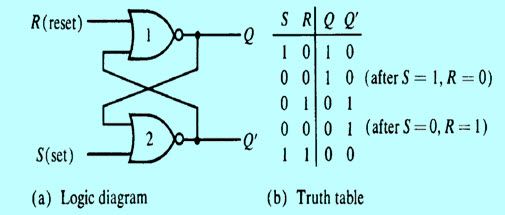

Tidligere ble utformingen av logikkretser kan gjøres ved hjelp av SSI (liten skala integrasjon) komponenter som logiske porter, multipleksere , de-multiplexere, FF, etc. Men nå kan en PLD erstatte alle disse SSI-komponentene. Så dette er grunnen til å redusere SSI-bransjen sammenlignet med PLD, og disse brukes i flere applikasjoner. De programmerbar logikkenhet eller PLD er en slags brikke som brukes til å implementere logikkretsen. Den inkluderer et sett med logiske kretselementer som kan modifiseres på flere måter. En PLD ser ut som en svart boks som består av programmerbare brytere samt logiske porter. Bryterens hovedfunksjon er å la logikkportene i PLD være assosiert med hverandre for å utføre logiske kretser. PLD er klassifisert i forskjellige typer, slik som SPLD-enkel PLD ( PLA & PAL ), CPLD-kompleks PLD , FPGA- feltprogrammerbare portarrays . Denne artikkelen diskuterer hva som er en PAL og PLA, design og deres forskjeller.

Hva er PAL og PLA?

Både Programmerbar Array Logic og Programmerbar logisk matrise er typer PLD (programmerbare logiske enheter), og disse brukes hovedsakelig for å designe kombinasjonslogikk gjensidig av sekvensiell logikk. Hovedforskjellen mellom disse to er at PAL kan utformes med en samling AND-porter og fast samling av OR-porter, mens PLA kan utformes med et programmerbart utvalg av AND selv om det er en fast samling av OR-port. En programmerbar logisk enhet tilbyr en enkel og fleksibel logikkretsdesign.

Programmerbar Array Logic

Tidligere til programmerbare logiske enheter, kombinasjonslogiske kretser kan utformes med multipleksere, og disse kretsene var stive så vel som sammensatte, så utvikles PLD. Den opprinnelige programmerbare logiske enheten var ROM, men den lyktes ikke på grunn av maskinvarespildproblemer samt eksponentiell vekstforbedring i alle maskinvareapplikasjoner. For å løse dette problemet ble PAL og PLA brukt. Disse to er programmerbare, og bruker maskinvaren effektivt.

Programmerbar logisk matrise

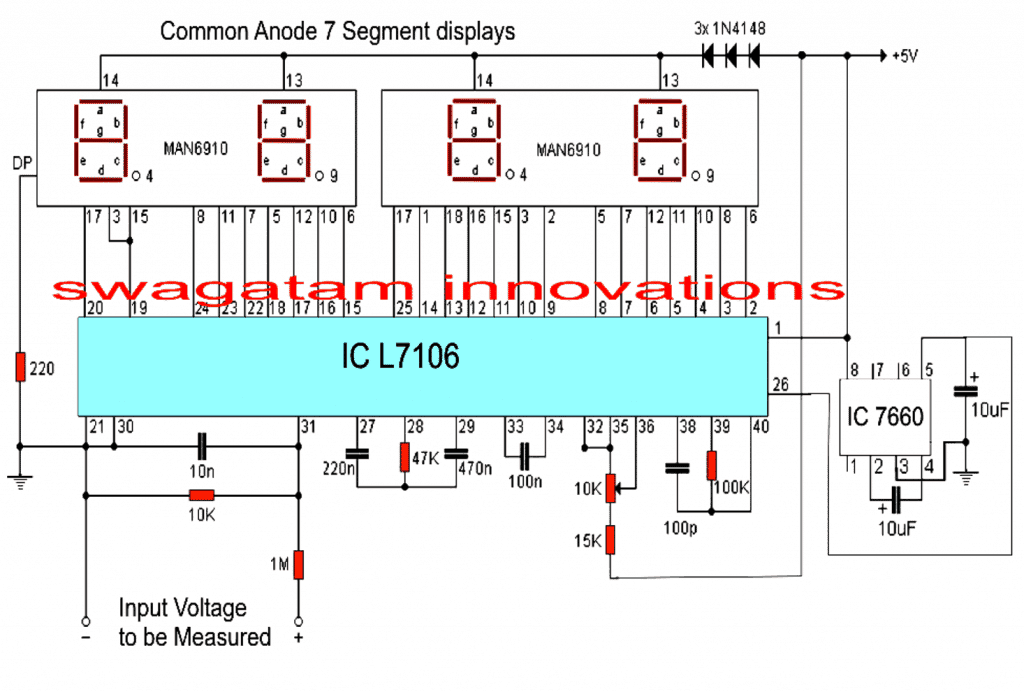

Design of Programmable Array Logic (PAL)

De definisjon av begrepet PAL eller Programmable Array Logic er en type PLD som er kjent som Programmable Logic Device circuit, og arbeidet med denne PAL er den samme som PLA. Utformingen av den programmerbare arraylogikken kan gjøres med faste ELLER porter så vel som programmerbare OG porter. Ved å bruke dette kan vi implementere to enkle funksjoner uansett hvor tilknytningene OG portene til hver ELLER port angir det høyeste antall produktforhold som kan produseres i form av SOP (sum av produkt) av en eksakt funksjon.

Da logikkportene som AND kontinuerlig er koblet til ELLER-portene, og det indikerer at det produserte produktbegrepet ikke distribueres med utgangsfunksjonene. Hovedtanken bak PLD-utvikling er å produsere en sammensatt boolsk logikk på en enkelt brikke ved å fjerne den defekte ledningen, unngå logikkdesignet, samt redusere strømforbruket.

Eksempel på PAL

Implementer følgende Boolsk uttrykk med hjelp av programmerbar array logikk (PAL)

X = AB + AC '

Y = AB ’+ BC’

Ovennevnte gitt to Boolske funksjoner er i form av SOP (sum av produkter) . Produktuttrykkene som er tilstede i de boolske uttrykkene er X & Y, og ett produktuttrykk som er AC er vanlig i hver ligning. Så de totale nødvendige logiske porter for å generere de ovennevnte to ligningene er OG porter-4 ELLER programmerbare porter-2. Det tilsvarende PAL-logikkdiagrammet er vist nedenfor.

PAL Logic Circuit

OG-portene som er programmerbare, har rett til inngang for både normale og komplementære variable innganger. I det ovennevnte logikkdiagrammet er de tilgjengelige inngangene for hver OG-port A, A ’, B, B’, C, C ’. Så, for å generere et enkelt produktbegrep med hver AND-gate, kreves programmet.

Alle produktbetingelsene kan fås ved inngangene til hver ELLER-port. Her kan de programmerbare forbindelsene på logikkporten betegnes med symbolet ‘X’.

Her er ELLER gateinngangene faste. Dermed er de nødvendige produktbetingelsene knyttet til hver ELLER gateinngang. Som et resultat vil disse portene generere bestemte boolske ligninger. De ‘.’ Symbolet representerer permanente forbindelser.

Design of Programmable Logic Array (PLA)

Definisjonen av begrepet PLA presenterer den boolske funksjonen i form av en sum av produktet (SOP). Utformingen av denne programmerbare logiske matrisen kan gjøres ved hjelp av logikkportene som AND, OR, og IKKE ved å produsere på brikken, noe som gjør at alle innganger, så vel som komplimentet, kan oppnås mot hver AND-gate.

Hver OG-portens utgang er koblet til hver ELLER-port. Til slutt genererer utgangen fra ELLER-porten utgangen fra brikken. Dermed er dette hvordan en passende assosiasjon er ferdig for å bruke uttrykkene for summen av produktet. I den programmerbare logiske matrisen er forbindelsene til logiske porter som AND & OR programmerbare. PLA er dyrt og vanskelig å sammenligne med PAL. PAL bruker to forskjellige utviklede metoder som kan brukes til en programmerbar logisk matrise for å forbedre enkelhet ved programmering. I denne typen metode kan enhver tilkobling gjøres ved å bruke en sikring på hvert skjæringspunkt, uansett hvor unødvendige tilkoblinger kan løsnes ved at sikringen går. Den siste teknikken involverer tilkobling mens fabrikasjonsprosessen bruker passende deksel som tilbys for den nøyaktige samtrafikkmodellen.

Eksempel på PLA

Implementere følgende boolske uttrykk ved hjelp av PLA (Programmable Logic Array)

X = AB + AC '

Y = AB '+ BC + AC'

Ovennevnte to boolske funksjoner er i form av SOP (sum av produkter). Produktuttrykkene som er tilstede i de boolske uttrykkene er X & Y, og ett produktuttrykk som er AC er vanlig i hver ligning. Så, de totale nødvendige logiske porter for å generere de ovennevnte to ligningene er OG porter-4, ELLER programmerbare ELLER porter-2. Det tilsvarende PLA-logikkdiagrammet er vist nedenfor.

PLA Logic Circuit

OG-portene som er programmerbare, har rett til inngang for både normale og komplementære variable innganger. I det ovennevnte logikkdiagrammet er de tilgjengelige inngangene for hver OG-port A, A ’, B, B’, C, C ’. Så, for å generere et enkelt produktbegrep med hver AND-gate, kreves programmet.

Alle produktbetingelsene kan fås ved inngangene til hver ELLER-port. Her kan de programmerbare forbindelsene på logikkporten betegnes med symbolet ‘X’.

Forskjellen mellom PAL og PLA

De Forskjellen mellom PAL og PLA i tabellform inkluderer hovedsakelig PAL og PLA fullform , konstruksjon, tilgjengelighet, fleksibilitet, pris, antall funksjoner og hastighet som er diskutert nedenfor.

| Programmerbar Array Logic (PAL) | Programmable Logic Array (PLA) |

| Den fulle formen for PAL er programmerbar array-logikk | Den fulle formen for PLA er en programmerbar logisk matrise |

| Konstruksjonen av PAL kan gjøres ved hjelp av den programmerbare samlingen av AND & OR-porter | Konstruksjonen av PLA kan gjøres ved hjelp av den programmerbare samlingen av OG & fast samling av ELLER porter. |

| Tilgjengeligheten av PAL er mindre produktiv | Tilgjengeligheten av PLA er mer |

| Fleksibiliteten til PAL-programmering er mer | Fleksibiliteten til PLA er mindre |

| Kostnaden for en PAL er dyr | Kostnaden for PLA er mellomklasse |

| Antall funksjoner implementert i PAL er stort | Antall funksjoner implementert i PLA er begrenset |

| PAL-hastigheten er treg | Hastigheten til PLA er høy |

Dermed handler dette om PAL og PLA. Av informasjonen ovenfor kan vi til slutt konkludere med at dette er de programmerbare logiske enhetene (PLD) der programmerbar logisk matrise er mer fleksibel enn programmerbar arraylogikk. Men programmerbar matrikklogikk kan uten problemer generere en kombinasjonslogisk krets. Her er et spørsmål til deg, hva er rollen til PAL og PLA innen digital elektronikk ?