En riktig beregnet MOSFET-på-prosess sikrer at enheten slås PÅ med optimal effektivitet.

Mens du utformet MOSFET-baserte kretser, har du kanskje lurt på hva som er riktig måte å slå på en MOSFET? Eller rett og slett hva er minimumsspenningen som skal brukes over porten / kilden til enheten for å slå den perfekt på?

Selv om dette for mange digitale systemer kanskje ikke er et problem, krever 5V-systemer som DSPer, FPGAer og Arduinos øke deres produksjon for optimal brytertilstand for tilkoblet MOSFET.

Og i disse situasjonene begynner designeren å se på spesifikasjonene til MOSFET for å få terskelspenningsdataene. Designeren antar at MOSFET vil slå PÅ og endre tilstand når dette terskelnivået krysses.

Dette kan imidlertid ikke være så enkelt som det kan se ut til å være.

Hva er terskelspenning VGS (th)

Først og fremst må vi innse at terskelspenningen, betegnet som VGS (th)er ikke for kretsdesignere å bekymre seg for.

For å være presis, er det portens spenning som får MOSFETs avløpsstrøm til å krysse et terskelnivå på 250 μA, og dette testes under forhold som normalt ikke vil oppstå i praktiske anvendelser.

Under visse analyser brukes en konstant 5V for ovennevnte testing av enheten. Men denne testen implementeres normalt med porten og avløpet på enheten som er koblet til eller kortsluttet med hverandre. Du kan enkelt få denne informasjonen i selve databladet, så det er ikke noe mystisk med denne testen.

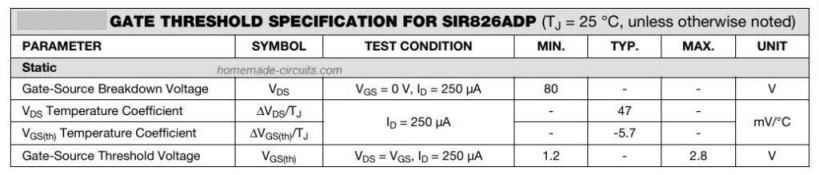

Tabellen ovenfor angir terskelnivåene og de relevante testbetingelsene for et eksempel på MOSFET.

For en ønsket applikasjon kan designeren være bekymret for en fryktet situasjon kjent som 'indusert' gate-spenning, noe som for eksempel kan være et alvorlig problem i en lav side MOSFET av synkron buck-omformer .

Som diskutert tidligere, må vi også her forstå at det å krysse terskelen VGS (th)nivået kan ikke tvinge enheten til å komme i en gjennombruddstilstand. Dette nivået forteller faktisk designeren om terskelen der MOSFET bare begynner å slå seg på, og er ikke en situasjon der ting bare slutter helt.

Det kan være tilrådelig at mens MOSFET er i avslått tilstand, holdes portens spenning under VGS (th)nivå, for å forhindre strømlekkasje. Men mens du slår den på, kan denne parameteren bare ignoreres.

Overfør karakteristisk kurve

Du finner et annet kurvediagram som heter overføringsegenskaper i MOSFET-datablad som forklarer hvordan den slår PÅ-oppførsel som svar på økende portspenning.

For å være presis kan dette være mer relatert til gjeldende variasjonsanalyse med hensyn til gate spenning og enhetens tilfelle temperatur. I denne analysen har VDSholdes på et fast nivå, men høyt nivå, rundt 15V, som kanskje ikke blir avslørt i databladets spesifikasjoner.

Hvis vi refererer til kurven som vist ovenfor, innser vi at for 3 A avløpsstrøm kan 3,2 V gate-til-kildespenning ikke være tilstrekkelig.

Kombinasjonen vil resultere i en VDS på 10 V, typisk med en spredning på 200 watt.

Overføringskurvedata kan være nyttige for MOSFET-er som opereres i det lineære området, men kurvedataene kan ha mindre betydning for MOSFET-er i bytteprogrammer.

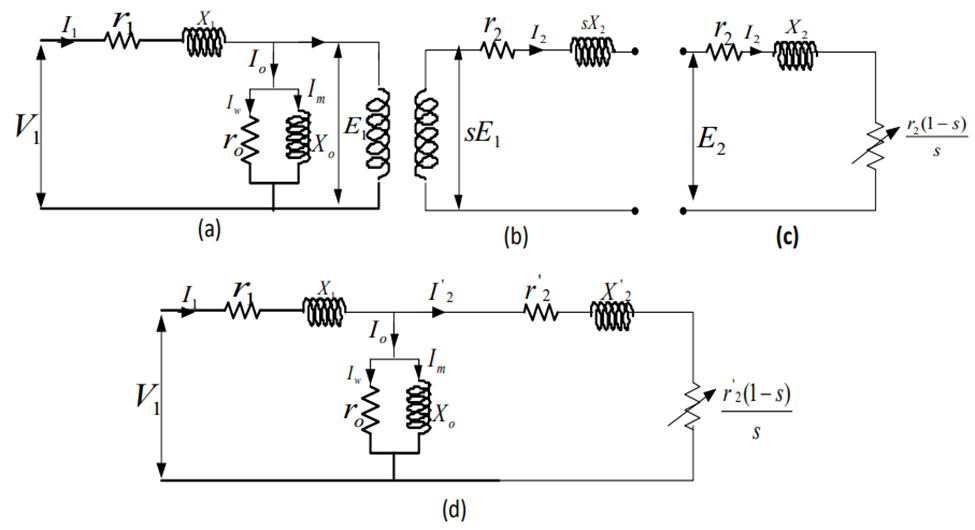

Produksjonsegenskaper

Kurven som avslører de faktiske dataene om MOSFETs full PÅ-tilstand er kjent som utgangskurven som vist nedenfor:

Her, for de forskjellige nivåene av VGSfremoverfallet til MOSFET måles som en funksjon av strømmen. Enhetsingeniører bruker disse kurvedataene for å bekrefte det optimale nivået på portens spenning.

For hvert nivå av gate spenning som sørger for en full innkobling av MOSFET [RDS (på)], får vi en rekke spenningsfall (V.GS) på tvers av avløp til kilde med strengt lineær respons med avløpsstrøm. Rekkevidden begynner fra null og oppover.

For spenninger med lavere port (V.GS) når avløpsstrømmen økes, finner vi at kurven mister den lineære responsen, beveger seg gjennom 'kneet' og deretter går flatt.

Ovennevnte kurvedetaljer gir oss de komplette utgangskarakteristikkene for en rekke portspenninger fra 2,5 V til 3,6 V.

MOSFET-brukere kan normalt tenke på dette som den lineære funksjonen. Imidlertid kan ingeniøringeniører foretrekke å være mer oppmerksomme på den grå regionen i grafen som antyder den nåværende metningsregionen for påført gate-spenning.

Den avslører gjeldende data som har berørt metningspunktet eller metningsgrensen. På dette punktet, hvis VDSer økt vil resultere i en marginal økning i strømmen, men en liten økning i avløpsstrømmen kan føre til en mye større VDS.

For økte spenningsnivåer i porten, som gjør at MOSFET kan slå seg PÅ helt, vil det grønne skyggelagte området vise operasjonspunktet for prosessen, indikert som resistiv (eller ohmisk) region.

Vær oppmerksom på at kurvene her bare viser de typiske verdiene, og ikke inkluderer noen minimums- eller maksimumsgrenser.

Når enheten arbeider ved lavere omgivelsestemperaturer, vil enheten kreve høyere portspenning for å holde seg i det resistive området, noe som kan gå oppover med en hastighet på 0,3% / ° C.

Hva er MOSFET RDS (på)

Når enhetsingeniører må møte utgangskarakteristikkene til MOSFET, vil de egentlig lære om RDS (på)av enheten med henvisning til de spesifikke driftsforholdene.

Generelt kan dette være en blanding av VGSog jegDSover området der kurven har avviket fra den rette linjen til den delen som er angitt av den grå skyggen.

Tatt i betraktning eksemplet som er diskutert ovenfor, en gate spenning på 3,1 V med en startstrøm på 10 ampere, vil ingeniørene vite at RDS (på)vil ha en tendens til å være større enn den estimerte verdien. Når det er sagt, forventer vi at MOSFET-produsenten skal gi omtrentlige data angående dette?

Med begge mengdene VDSog jegDSlett oppnåelig i kurven kan det bli for fristende, og ofte overgis til, for å dele de to størrelsene på den resulterende RDS (på).

Dessverre har vi ikke en RDS (på)for vurderingen her. Det ser ut til å være utilgjengelig for de nevnte situasjonene siden for noen del av lastelinje å representere en motstand må krysse gjennom opprinnelsen på en lineær måte.

Når det er sagt, kan det være mulig å simulere lastelinjen i en samlet form som en ikke-lineær motstand.

I det minste vil dette garantere at enhver forståelse av praktisk arbeid opprettholdes ved opprinnelsen (0, 0).

Gate Charge Curve-egenskaper

Det er portladekurvedataene som faktisk gir oss et reelt hint om spesifikasjonene for å slå på MOSFET som vist i figuren nedenfor :

Selv om kurven ovenfor er en standard inkludering i alle MOSFET-datablad, blir de underliggende indikasjonene sjelden forstått av MOSFET-brukeren.

Videre krever den moderne fremgangen i MOSFET-layoutene, som grøft og skjermede porter, en revidert adressering av dataene.

For eksempel kan spesifikasjonen kalt 'gate-charge' virke litt misvisende av seg selv.

De lineære og delte delene av kurven ser ikke ut som spenningslading av en kondensator, uavhengig av hvor mye ikke-lineær verdi den kan ha.

For å være presis, indikerer portladningskurven en tilknyttet data for to ikke-parallelle kondensatorer, som har forskjellige størrelser og bærer forskjellige spenningsnivåer.

I teorien er funksjonell kapasitans som bevist fra MOSFET gate terminal definert med ligningen:

Ciss= Cgs+ Cgd

hvor Ciss= portkapasitans, Cgs= portkildekapasitans, Cgd= portavløpskapasitet

Selv om det kan virke ganske enkelt å måle denne enheten og spesifisere i databladene, må det bemerkes at begrepet Cisser faktisk ikke en reell kapasitans.

Det kan være helt galt å tro at en MOSFET er slått PÅ bare gjennom en spenning som påføres portens kapasitans Ciss'.

Som angitt i figuren ovenfor, rett før en MOFET slår seg på, har portkapasitansen ingen ladning, men kapasitansen ved portavløpet Cgdhar en negativ ladning som må elimineres.

Begge disse kapasitansene har en ikke-lineær natur, og deres verdier varierer i stor grad ettersom de påførte spenningene varierer.

Derfor er det viktig å merke seg at det er de lagrede ladningene til MOSFET som bestemmer bytteegenskapene, og ikke kapasitansverdien for et spesifikt spenningsnivå.

Siden de to kapasitanselementene som utgjør Cisshar forskjellige fysiske egenskaper, har de en tendens til å bli ladet med forskjellige spenningsnivåer, og krever at MOSFET-prosessen også slås på gjennom to trinn.

Den presise sekvensen kan være forskjellig for resistive og induktive applikasjoner, men vanligvis er de fleste praktiske belastningene svært induktive, prosessen kan simuleres som vist i følgende figur:

Gate Charge Timing Sequence

Gate charge timing-sekvensene til MOSFET kan studeres fra diagrammet nedenfor:

Det kan forstås med følgende forklaring:

- T0 - T1: Cgsladninger fra null til VGS (th)... VDSeller jegDSgår ikke gjennom noen endringer.

- T1-T2, begynner strømmen å stige i MOSFET som svar på den økende portspenningen fra V.GS (th)opp til platåspenningen Vgp.

- Her øker IDS og når til full belastningsstrøm fra 0 V, selv om VDSforblir upåvirket og konstant. Den tilhørende ladningen dannes gjennom integralen av Cgsfra 0 V til V.gp, og Qgsgitt i databladene.

- T2 - T3: Observer det flate området mellom T2 og T3, det heter Miller-platået.

- Før bryteren PÅ, Cgdlader og holder opp til forsyningsspenningen VI, til jegDSnår toppverdien I (belastning) ved T2.

- Tiden mellom perioden T2 og T3, den negative ladningen (VI- Vgp) blir omgjort til positiv ladning med hensyn til platåspenningen Vgp.

- Dette kan også visualiseres som fallet av avløpsspenningen fra V.Itil omtrent null.

- Ladningen involvert er lik Cgdintegrert fra 0 til V.i, som er vist som Qgdi datablad.

- Under T3 - T4 klatrer portens spenning fra V.gptil VGS, og her finner vi knapt noen endring for VDSog jegDS, men den effektive RDS (på)synker litt når portens spenning stiger. På noe spenningsnivå over V.gp, gir produsentene nok tillit til å fastsette den øvre grensen for effektiv RDS (på).

For induktive belastninger

Strømøkningen i MOSFET-kanalen på grunn av en induktiv belastning må fullføres før spenningen begynner å synke.

Ved starten av platået er MOSFET i AV-tilstand, i nærvær av høy strøm og spenning over avløp til kilde.

Mellom tiden T2 og T3, en ladning Qgdpåføres porten til MOSFET, hvor MOSFET-karakteristikken transformerer fra konstant strøm til konstant motstandsmodus på slutten.

Når overgangen ovenfor skjer, blir det ikke merkbar endring i portens spenning V.gptar plass.

Dette er grunnen til at det aldri er noen lurt ide å relatere en MOSFET PÅ-prosess med et bestemt nivå av portspenning.

Det samme kan være sant for OFF-prosessen, som krever at de samme to ladningene (diskutert tidligere) elimineres fra porten til MOSFET i motsatt rekkefølge.

MOSFET Byttehastighet

Mens Qgspluss Qgdsammen sørger for at MOSFET slås PÅ helt, det forteller oss ikke om hvor raskt dette vil skje.

Hvor raskt strømmen eller spenningen vil skifte bestemmes av hastigheten som ladelementene ved porten påføres eller fjernes. Dette blir også betegnet som portdrivstrømmen.

Selv om en rask økning og fallhastighet sikrer lavere koblingstap i MOSFET, kan disse også gi opphav til komplikasjoner på systemnivå relatert til økte toppspenninger, svingninger og elektromagnetisk forstyrrelse, spesielt under avstengning av øyeblikkelig induktiv belastning.

Den lineært fallende spenningen som er vist i figur 7 ovenfor, klarer å ta en konstant verdi på Cgd, noe som knapt kan skje med MOSFET i praktiske anvendelser.

For å være presis, portdreneringsladningen Cgdfor et høyspennings superkryss viser MOSFET som SiHF35N60E en betydelig høy lineær respons, som det kan sees følgende figur:

Variasjonsområdet som eksisterer i verdien av Crss(omvendt overføring) er mer enn 200: 1 innen de innledende 100 V. På grunn av dette ser den faktiske falltiden for spenning mot portladningskurven mer ut som den stiplede linjen vist i rød farge i figur 7.

Ved høyere spenninger er økningen og fallet av ladningene sammen med deres ekvivalente dV / dt-verdier mer avhengige av verdien av Crss, i stedet for integralen av hele kurven indikert som Qgd.

Når brukere vil sammenligne MOSFET-spesifikasjoner i forskjellige designmiljøer, bør de innse at MOSFET med halv Qgdverdien vil ikke nødvendigvis inneholde to ganger raskere byttehastighet, eller 50% mindre byttetap.

Dette er ifølge Cgdkurve og dens styrke ved høyere spenninger, kan det være ganske mulig for en MOSFET å ha et lavt Qgd i databladet, men uten noen økning i byttehastigheten.

Oppsummering

I den faktiske implementeringen skjer aktivering av en MOSFET gjennom en rekke prosesser, og ikke med en forhåndsbestemt parameter.

Kretsdesignere må slutte å forestille seg at VGS (th), eller spenningsnivåer kan brukes som portspenning for å bytte MOSFET-utgang fra høy til lav RDS (på).

Det kan være nytteløst å tenke på å ha en RDS (på)under eller over et spesifikt spenningsnivå i porten, siden portens spenningsnivå ikke i utgangspunktet bestemmer at MOSFET slås PÅ. Snarere er det anklagene Qgsog Qgdintrodusert i MOSFET som utfører jobben.

Du kan oppleve at portens spenning stiger over V.GS (th)og Vgpunder lade / utladningsprosessen, men disse er ikke så viktige.

På samme måte kan hvor raskt MOSFET i dag kan slå PÅ eller AV, være en kompleks funksjon av Qgseller Qgd.

For å evaluere MOSFET-koblingshastigheter, spesielt de avanserte MOSFETene, må designeren gå gjennom en omfattende studie om portladekurven og kapasitanskarakteristikken til enheten.

Referanse: https://www.vishay.com/

Forrige: Overføringsegenskaper Neste: TL494 Dataark, Pinout, Application Circuits