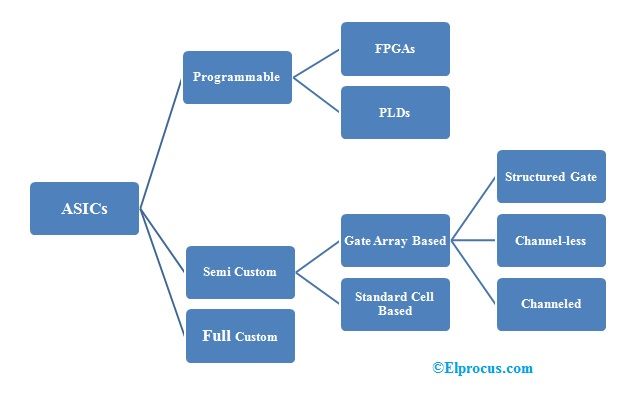

Den største ulempen med kombinasjonskrets er, det bruker ikke noe minne for å lagre nåværende og tidligere tilstander. Derfor har den forrige inngangstilstanden ingen effekt på kretsens nåværende tilstand. Mens sekvensiell krets har minne, slik at utgangen kan variere basert på inngangen. Denne typen kretser bruker tidligere inngang, utgang, klokke og et minneelement. Her kan minneelementene være lås eller flip-flops. Sekvensielle kretser er designet av forskjellige metoder, for eksempel ved bruk av ROM og flips, PLA, CPLDs (Complex Programmable Logic Device) , FPGAer (feltprogrammerbar gate matrise) . I denne artikkelen skal vi bare diskutere hvordan du designer en sekvensiell krets ved hjelp av PLA.

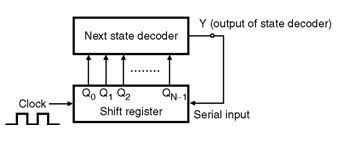

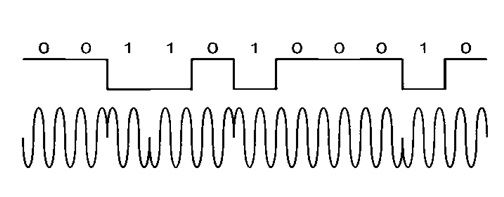

Blokkdiagrammet for sekvensiell krets som vist nedenfor:

Blokkdiagram over sekvensiell krets

Utforming av sekvensiell krets ved bruk av PLA

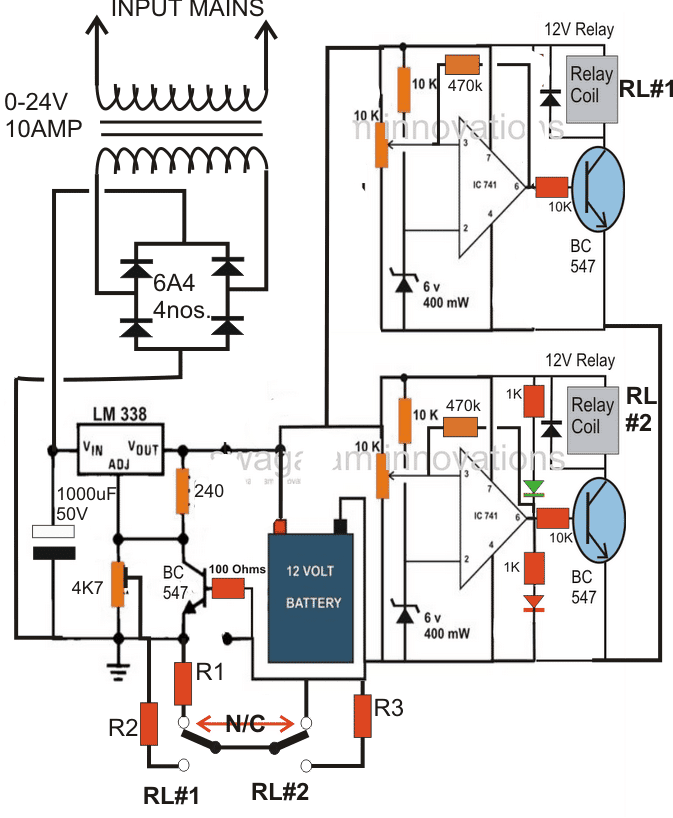

Sekvensielle kretser kan realiseres ved hjelp av PLAer (Programmable Logic Arrays) og flip-flops. I denne utformingen kan tilstandsoppdraget være viktig fordi bruken av en god tilstandsoppgave kan redusere det nødvendige antall produktuttrykk og dermed redusere den nødvendige størrelsen på PLA. Et produktuttrykk definert som sammenhengen mellom bokstavene, der hver bokstav er enten en variabel eller dens negasjon.

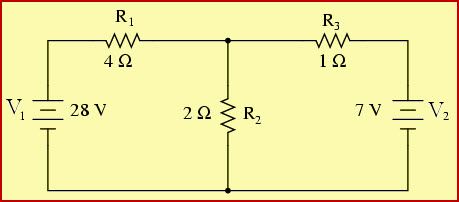

For la oss betrakte designet som en kodeomformer. Tilstandstabellen vist nedenfor i tabellen kan realiseres ved å bruke en PLA og tre flip-flops som vist under figuren. Denne kretskonfigurasjonen ligner veldig på ROM-flip-flop-basert design, bortsett fra at ROM erstattes av PLA av passende størrelse. Statens oppdrag fører til sannhetstabellen gitt nedenfor. Denne tabellen kan lagres i en PLA med fire innganger, 13 produktbetingelser og fire utganger, men dette vil gi lite redusert størrelse sammenlignet med 16-ords ROM.

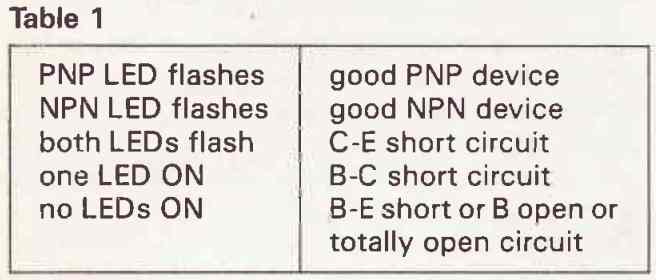

| X Q1 Q2 Q3 | Med D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

Tabell: Sannhetstabell

TILSTEDE STAT

| NESTE STAT X = 0 1 | TILSTEDE UTGANG (Z) |

| TIL | B C | 1 0 |

B C | D E Og E | 1 0 0 1 |

D ER | H H H M | 0 1 1 0 |

H M | A A TIL - | 0 1 1 - |

Tabell: Statstabell

Utforming av sekvensielle kretser ved bruk av PLA

Inngangsutgangslikninger avledet av Karnaugh Map

Her, da det er syv stater, kreves tre D-flip-flops. Dermed kreves en PLA-krets med 4 innganger og 4 utganger. Hvis tilstandsoppgaven til kodeomformeren vurderes, kan den resulterende utgangsligningen og D flip-flop-inngangsligninger avledet fra Karnaugh skrives følgende ligninger

D1 = Q1 + = Q2 ”

D2 = Q2 + = Q2 ”

D3 = Q3 + = Q1 Q2 Q3 = X ”Q1 Q3” = X Q1 ”Q2”

Z = X ”Q3” + X Q3

| X Q1 Q2 Q3 | Med D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 elleve

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

PLA-tabellen som tilsvarer disse ligningene er gitt i tabellen ovenfor. Denne tabellen kan realiseres ved å bruke PLA med fire innganger, syv produkttermer og fire utganger. For å verifisere driften av ovennevnte design, antar du at X = 0 og Q1Q2Q3 = 000. Dette velger rader - - 0- og 0 - - -0 i tabellen, så Z = 0 og D1D2D3 = 100. Etter den aktive klokkekanten er Q1Q2Q3 = 100. Hvis neste inngang er X = 1, velges rader - - 0 - og - 1- -, så Z = 0 og D1D2D3 = 110. Etter den aktive klokkekanten er Q1Q2Q3 = 110.

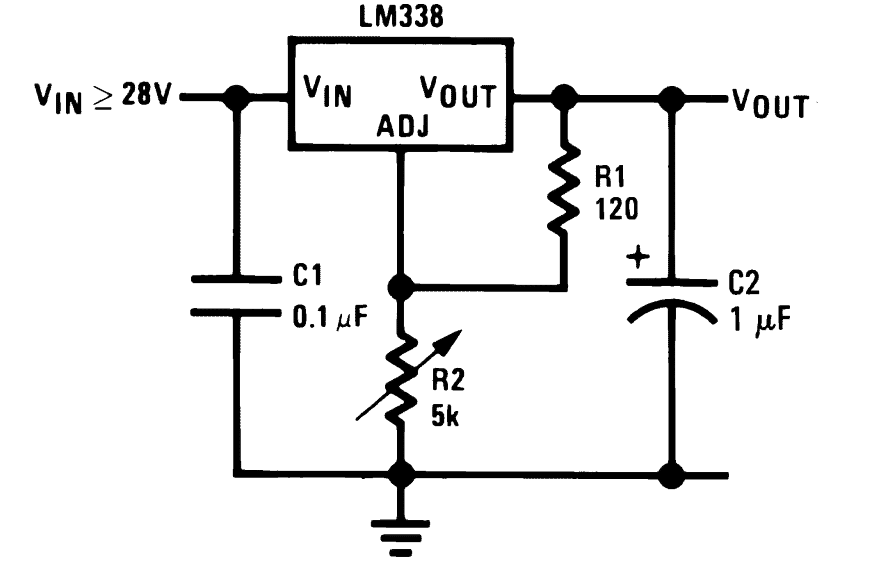

Programmable Logic Array (PLA)

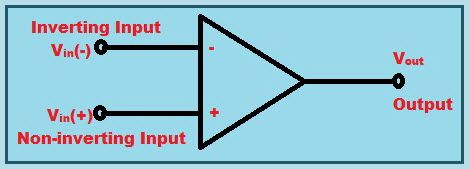

Programmable Logic Array er en programmerbar logisk enhet. Det brukes vanligvis til å implementere kombinasjonslogiske kretser. PLA har et sett med programmerbare AND-plan (AND-array), som lenker til et sett med programmerbare OR-plan (OR-array), som deretter kan suppleres foreløpig for å produsere en utgang. Dette oppsettet gjør det mulig å syntetisere et stort antall logiske funksjoner i sum av produkter (SOP) kanoniske former. Et enkelt blokkdiagram over en PLA er gitt nedenfor.

Blokkdiagram over en PLA

Hovedforskjellen mellom PLA og PAL (programmerbar array logikk) er,

PLA: Begge deler OG fly og ELLER fly er programmerbare.

PAL: Bare OG-planet er programmerbart, mens OR-planet er fast.

For bedre forståelse av PLA, vurderer vi eksemplet nedenfor.

La oss prøve å implementere disse funksjonene f1 og f2 er gitt som

Innganger x1, x2, x3 og deres respektive komplementerte signaler blir gitt til programmerbare OG-plan, der vil vi få OG-planutganger som P1, P2, P3-kalt mintermer. Deretter blir disse signalene gitt til programmerbart ELLER plan for å produsere nødvendig utgangsfunksjon f1 og f2 (sum av produkter). Figuren nedenfor beskriver gate-nivå implementering av PLA for gitt funksjonalitet.

Implementering av PLA

Dette handler om å designe sekvensielle kretser ved hjelp av PLA. Vi anser at informasjonen i denne artikkelen er nyttig for deg til en bedre forståelse av dette konseptet. Videre, spørsmål angående denne artikkelen eller hjelp til gjennomføring av elektriske og elektroniske prosjekter , kan du nærme oss ved å kommentere i kommentarfeltet nedenfor. Her er et spørsmål til deg, Hva menes med en sekvensiell krets?