Designprosessen for digital maskinvare har forvandlet seg intenst de siste årene. Så små digitale kretser kan implementeres ved hjelp av PAL og PLA. Hver enhet brukes å implementere forskjellige kretser som ikke trenger mer enn antall i / ps, o / ps og produktbetingelser som tilbys i den spesifikke brikken. Disse sjetongene er utilstrekkelige til ganske beskjedne størrelser, og støtter normalt et gjensidig antall innganger og utganger på ikke mer enn 32. For å designe disse kretsene som trenger flere innganger og utganger, kan enten mange PLAer / PALer brukes eller ellers en mer stilig type av chip kan brukes kalt en CPLD (kompleks programmerbar logisk enhet). En CPLD-brikke inkluderer flere kretsblokker på en enkelt brikke med innvendige ledningsressurser for å feste kretsblokkene. Hver kretsblokk kan sammenlignes med en PLA eller en PAL.

Hva er en kompleks programmerbar logisk enhet?

Forkortelsen til CPLD er 'Komplekse programmerbare logiske enheter', det er en slags integrert krets at applikasjonsdesignere designer for å implementere digital maskinvare som mobiltelefoner. Disse kan håndtere bevisst høyere design enn SPLDs (enkle programmerbare logiske enheter), men gir mindre logikk enn FPGAs ( feltprogrammerbare portarrayer CPLDs inkluderer mange logiske blokker hver av blokkene inneholder 8-16 makroceller. Fordi hver logikkblokk utfører en bestemt funksjon, er alle makrocellene i en logikkblokk fullt tilkoblet. Avhengig av bruken kan disse blokkene være koblet til hverandre eller ikke.

Kompleks programmerbar logisk enhet

De fleste CPLDer (komplekse programmerbare logiske enheter) har makroceller med en sum av logikkfunksjon og et valgfag FF (flip-flop) . Avhengig av brikken støtter den kombinatoriske logikkfunksjonen fra 4 til 16 produkttermer med inkluderende fan-in. CPLDs er også forskjellige når det gjelder skiftregistre og logiske porter. På grunn av dette kan CPLD-er med et stort antall logiske porter brukes i stedet for FPGA-er. En annen CPLD-spesifikasjon betyr antall produktuttrykk som en makrocell kan oppnå. Produktbetingelser er et produkt av digitale signaler som utfører en spesifikk logikkfunksjon.

CPLD er tilgjengelig i flere IC-pakkeskjemaer og logiske familier. CPLD-er varierer også når det gjelder forsyningsspenning, driftsstrøm, standbystrøm og strømforsyning. I tillegg kan disse fås med forskjellige mengder minne og forskjellige typer minnestøtte. Vanligvis uttrykkes minne i bits / megabit. Minnestøtte består av ROM, RAM og dual-port RAM. Den består også av CAM (innholdsadresserbart minne) samt FIFO (først inn, først ut) minne og LIFO (siste inn, siste ut) minne.

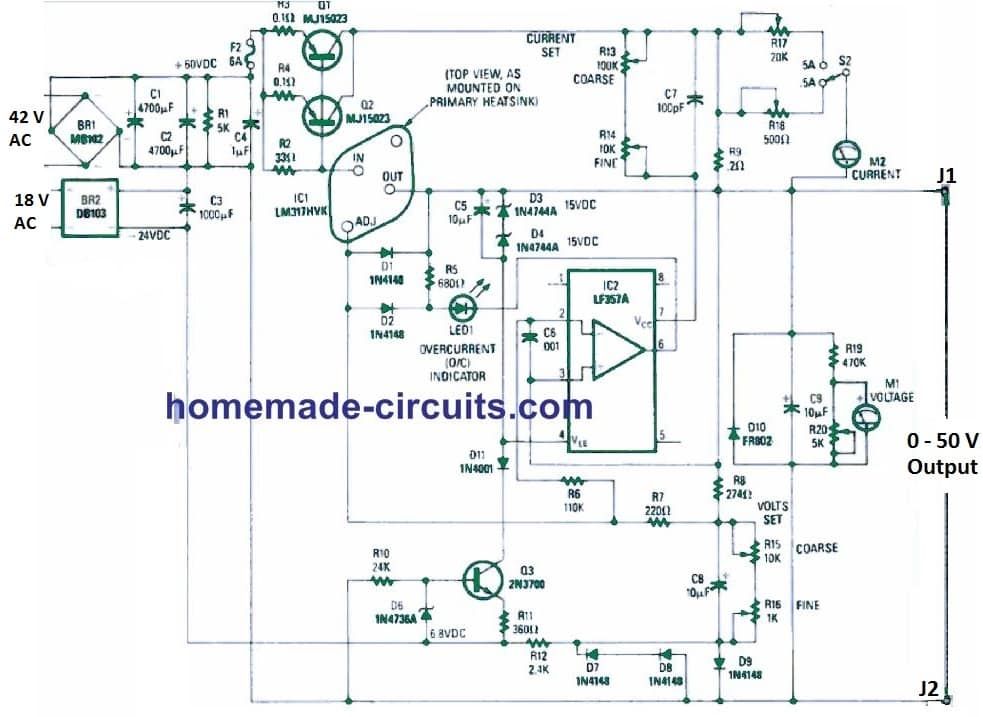

Arkitektur av komplekse programmerbare logiske enheter

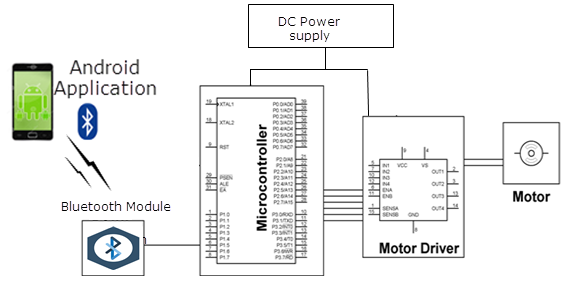

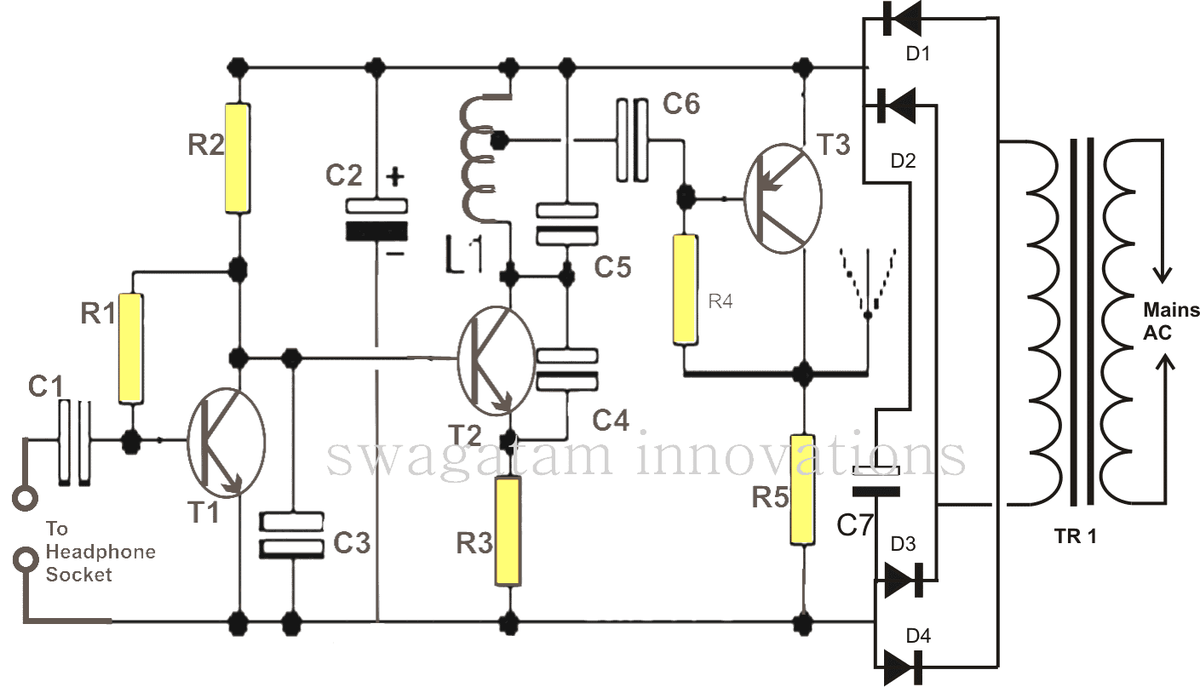

En kompleks programmerbar logisk enhet består av en gruppe programmerbare FB (funksjonsblokker). Inngangene og utgangene til disse funksjonelle blokkene er koblet sammen av en GIM (global samtrafikkmatrise). Denne samtrafikkmatrisen kan omkonfigureres, slik at vi kan endre kontaktene mellom funksjonsblokkene. Det vil være noen inngangs- og utgangsblokker som lar oss forene CPLD til den eksterne verdenen. Arkitekturen til CPLD er vist nedenfor.

Vanligvis ser den programmerbare FB ut som rekke logiske porter , hvor en rekke OG-porter kan programmeres og ELLER porter er stabile. Men hver produsent har sin måte å tenke på å designe den funksjonelle blokken. En oppført o / p kan bli funnet ved å betjene tilbakemeldingssignalene oppnådd fra ELLER portutgangene.

CPLD Arkitektur

I CPLD-programmering blir designet først kodet på Verilog- eller VHDL-språk når koden er (simulert og syntetisert. Under syntesen blir CPLD-modellen (målenhet) håndplukket og en teknologibasert kartnettliste produseres. Denne listen kan være nær -tilpasning til den ekte CPLD-arkitekturen ved hjelp av en sted- og ruteprosess, vanligvis oppnådd av sted-og-rute-programvaren til CPLD Company's proprietære. Da vil operatøren gjøre noen bekreftelsesprosesser. Hvis alt er bra, vil han bruke CPLD, ellers han vil omorganisere det.

Arkitekturproblemer av CPLD

Når du vurderer en kompleks programmerbar logisk enhet for bruk i design, er det noen arkitekturproblemer som kan tas i betraktning

- Programmeringsteknologien

- Funksjonsblokkfunksjonen

- I / O-muligheten

Noen av familiene til CPLD fra forskjellige forhandlere inkluderer

- Altera MAX 7000 og MAX 9000 familier

- Atmel ATF- og ATV-familier

- Gitter isp LSI familie

- Gitter (Vantis) MACH-familien

- Xilinx XC9500-familien

Familier av CPLD

Anvendelser av CPLD

Applikasjonene til CPLD inkluderer følgende

- Komplekse programmerbare logiske enheter er ideelle for applikasjoner med høy ytelse og kritiske kontroller.

- CPLD kan brukes i digital design for å utføre funksjonene til boot loader

- CPLD brukes til å laste konfigurasjonsdataene til et feltprogrammerbart gate-array fra ikke-flyktig minne.

- Vanligvis brukes disse i små designapplikasjoner som adressekoding

- CPLD brukes ofte mange applikasjoner som i kostnadsfølsomme, batteridrevne bærbare enheter på grunn av den lave størrelsen og bruken av lav strøm.

Dermed handler alt om kompleks programmerbar logisk enhetsarkitektur og dens applikasjoner. Vi håper at du har fått en bedre forståelse av dette konseptet. Videre, eventuelle spørsmål angående dette konseptet eller å gjennomføre elektriske og elektroniske prosjekter , vennligst gi dine verdifulle forslag ved å kommentere i kommentarfeltet nedenfor. Her er et spørsmål til deg, hva er forskjellen mellom CPLD og FPGA?

Fotokreditter:

- CPLD wikimedia

- Arkitektur av CPLD lysbildesharecdn