MOS-transistoren er det mest grunnleggende elementet i storskala integrerte kretsdesign. Disse transistorene er generelt klassifisert i to typer PMOS og NMOS. Kombinasjonen av NMOS- og PMOS-transistorer er kjent som en CMOS transistor . Forskjellen logiske porter & andre digitale logiske enheter som er implementert må ha PMOS-logikk. Denne teknologien er billig og har god motstand mot forstyrrelser. Denne artikkelen diskuterer en av typene MOS-transistorer som en PMOS-transistor.

Hva er PMOS-transistor?

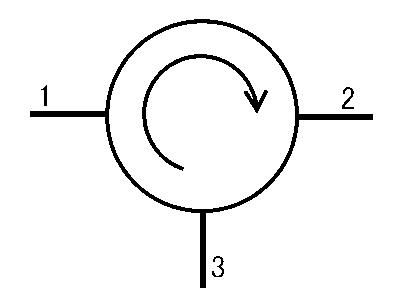

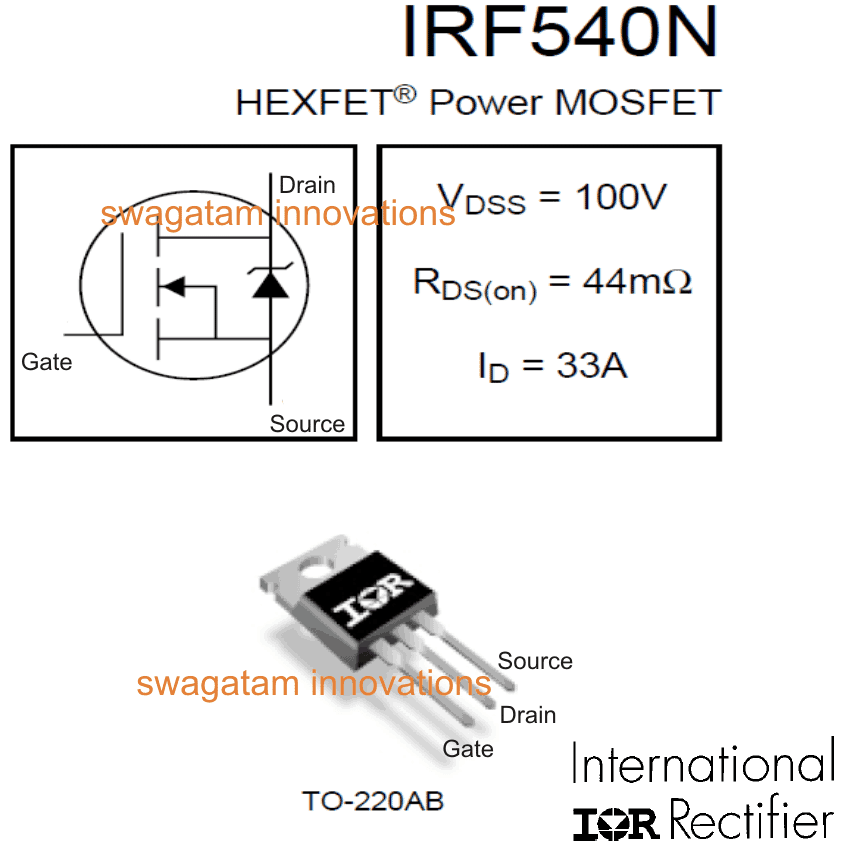

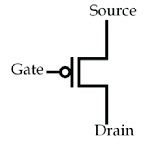

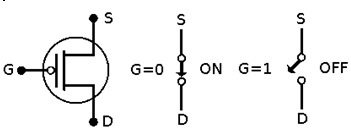

PMOS-transistoren eller P-kanal metalloksyd-halvlederen er en slags transistor der p-type dopingmidler brukes i kanal- eller portområdet. Denne transistoren er nøyaktig det motsatte av NMOS-transistoren. Disse transistorene har tre hovedterminaler; kilden, porten og avløpet der transistorens kilde er designet med et p-type substrat, og avløpsterminalen er designet med et n-type substrat. I denne transistoren er ladningsbærerne som hull ansvarlige for ledningen av strøm. PMOS-transistorsymbolene er vist nedenfor.

Hvordan fungerer PMOS-transistor?

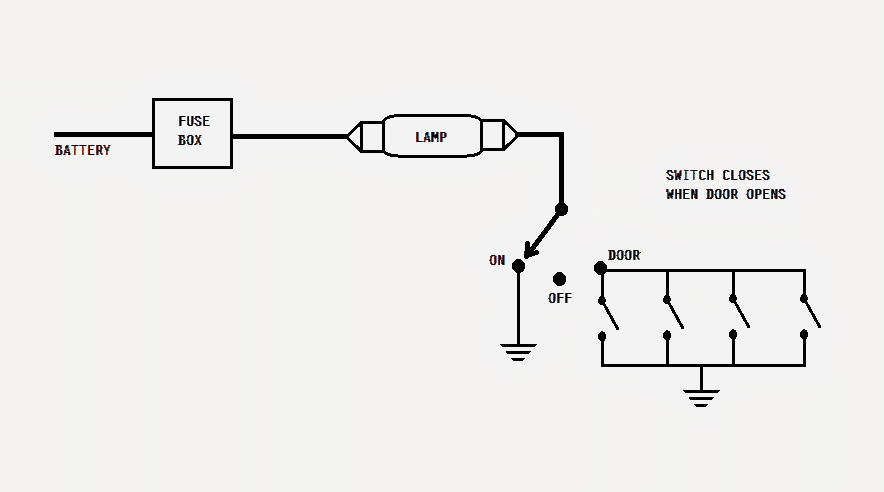

P-type transistoren fungerer er helt motsatt av n-type transistoren. Denne transistoren vil danne en åpen krets når den får ikke-ubetydelig spenning, noe som betyr at det ikke er noen strøm av elektrisitet fra porten (G) terminalen til kilden (S). På samme måte danner denne transistoren en lukket krets når den får en spenning på rundt 0 volt, noe som betyr at strømmen flyter fra gate (G) terminalen til drain (D).

Denne boblen er også kjent som en inversjonsboble. Så hovedfunksjonen til denne sirkelen er å invertere inngangsspenningsverdien. Hvis portterminalen gir en spenning på 1, vil denne omformeren endre den til null og fungerer kretsen deretter. Så funksjonen til PMOS-transistoren og NMOS-transistoren er helt motsatt. Når vi slår dem sammen til en enkelt MOS-krets, vil den bli en CMOS-krets (komplementær metalloksyd-halvleder).

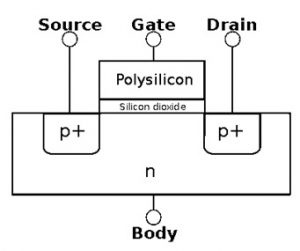

Tverrsnitt av PMOS-transistor

Tverrsnittet av PMOS-transistoren er vist nedenfor. En pMOS-transistor er bygget med en n-type kropp som inkluderer to p-type halvlederområder som er ved siden av porten. Denne transistoren har en kontrollerende port som vist i diagrammet som kontrollerer elektronstrømmen mellom de to terminalene som source & drain. I pMOS-transistoren holdes kroppen på +ve spenning. Når portterminalen er positiv, er kilde- og avløpsterminalene omvendt forspent. Når dette skjer, er det ingen strøm, så transistoren vil bli slått AV.

Når spenningsforsyningen ved portterminalen senkes, vil positive ladningsbærere bli tiltrukket til bunnen av Si-SiO2-grensesnittet. Når spenningen blir tilstrekkelig lav, vil kanalen bli invertert og skaper en ledende bane fra kildeterminalen til avløpet ved å tillate strømmen.

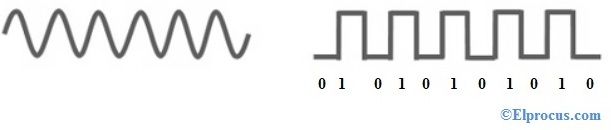

Når disse transistorene arbeider med digital logikk, har de vanligvis to forskjellige verdier bare som 1 og 0 (PÅ og AV). Transistorens positive spenning er kjent som VDD som representerer den logiske høye (1) verdien i digitale kretser. VDD-spenningen nivåer inn TTL logikk var generelt rundt 5V. Foreløpig tåler ikke transistorer så høye spenninger fordi de typisk varierer fra 1,5V – 3,3V. Lavspenningen er ofte kjent som GND eller VSS. Så VSS betyr logikken '0', og den er også satt normalt til 0V.

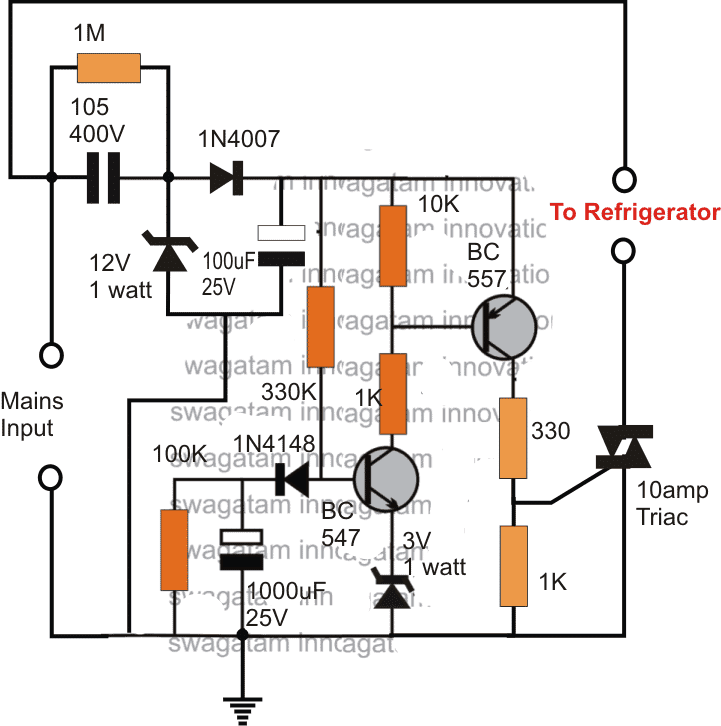

PMOS transistorkrets

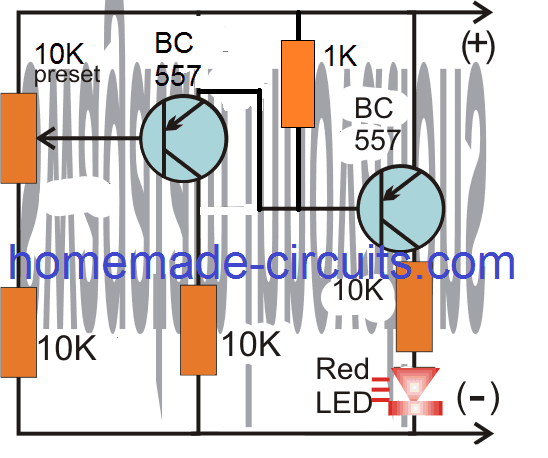

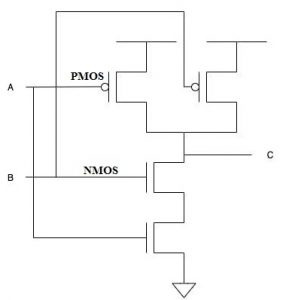

NAND-portdesignet som bruker PMOS-transistoren og NMOS-transistoren er vist nedenfor. Generelt er en NAND-port i digital elektronikk en logisk port som også kalles en IKKE-OG-port. Utgangen til denne porten er lav (0) bare hvis de to inngangene er høye (1) og dens utgang er et komplement til en OG-port. Hvis noen av de to inngangene er LAV (0), gir det høye utgangsresultater.

I den logiske kretsen nedenfor, hvis inngangen A er 0 og B er 0, vil en inngang på pMOS produsere '1' og en inngang på nMOS vil produsere '0'. Så denne logiske porten genererer en logisk '1' fordi den er koblet til kilden med en lukket krets og løsrevet fra GND gjennom en åpen krets.

Når A er '0' og B' er '1', vil en inngang til pMOS generere en '1' og en inngang til NMOS vil generere en '0'. Dermed vil denne porten produsere en logisk en fordi den er koblet til kilden gjennom en lukket krets og løsrevet fra GND av en åpen krets. Når A er '1' og B er '0', vil 'B'-inngangen til pMOS generere høy utgang (1) og 'B'-inngangen til NMOS vil generere en utgang så lav (0). Så denne logiske porten vil generere en logisk 1 fordi den er koblet til kilden gjennom en lukket krets og løsrevet fra GND av en åpen krets.

Når A er '1' og B er '1', vil en inngang på' pMOS produsere en null, og en inngang på nMOS vil generere '1'. Følgelig bør vi også verifisere B-inngangen til pMOS og nMOS. B-inngangen til pMOS vil generere en '0' og B-inngangen til nMOS vil generere en '1'. Så denne logiske porten vil generere en logisk '0' fordi den er løsrevet fra kilden av en åpen krets og er koblet til GND gjennom en lukket krets.

Sannhetstabell

Sannhetstabellen til den ovennevnte logiske kretsen er gitt nedenfor.

|

EN |

B |

C |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

Terskelspenningen til PMOS-transistoren er normalt 'Vgs' som er nødvendig for å lage kanalen kjent som kanalinversjon. I en PMOS-transistor er substratet og kildeterminalene ganske enkelt koblet til 'Vdd'. Hvis vi begynner å redusere spenningen ved å referere til kildeterminalen ved gateterminalen fra Vdd til et punkt hvor enn du legger merke til kanalinversjonen, ved denne posisjonen hvis du analyserer Vgs og kilden er på det høye potensialet, vil du få en negativ verdi. Så PMOS-transistoren har en negativ femte verdi.

PMOS-fabrikasjonsprosess

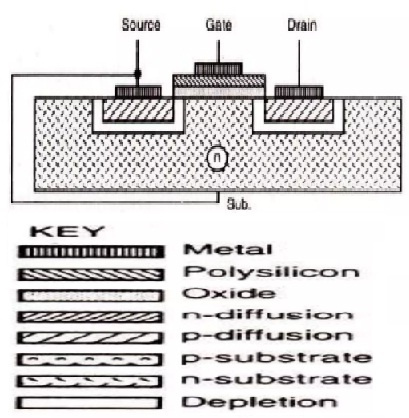

Trinnene involvert i PMOS-transistorfabrikasjon er diskutert nedenfor.

Trinn 1:

Et tynt silisiumwaferlag endres til N-type materiale ved ganske enkelt å dope fosformateriale.

Steg 2:

Et tykt silisiumdioksid (Sio2) lag dyrkes på et komplett p-type substrat.

Trinn 3:

Nå er overflaten belagt med en fotoresist over det tykke silisiumdioksidlaget.

Trinn 4:

Etter det blir dette laget ganske enkelt eksponert for UV-lys gjennom en maske som definerer de områdene der diffusjon skal finne sted sammen med transistorkanaler.

Trinn 5:

Disse områdene er etset bort gjensidig med det underliggende silisiumdioksydet slik at overflaten av skiven blir eksponert innenfor vinduet som er definert av masken.

Trinn 6:

Den gjenværende fotoresisten løsnes og tynt Sio2-lag dyrkes typisk 0,1 mikrometer over hele overflaten av brikken. Etter det legges polysilisium over dette for å danne strukturen til porten. En fotoresist er plassert over hele polysilisiumlaget og eksponerer UV-lys gjennom masken2.

Trinn 7:

Diffusjoner oppnås gjennom waferoppvarming til maksimal temperatur og passerer gass med ønskede p-type urenheter som bor.

Trinn 8:

En 1-mikrometer tykkelse silisiumdioksid dyrkes og fotoresistmateriale avsettes på den. Eksponer det ultrafiolette lyset med maske3 på de foretrukne områdene av porten, kilden og avløpet som er etset for å få kontaktkutt.

Trinn 9:

Nå er et metall eller aluminium avsatt over overflaten med en tykkelse på 1 mikrometer. Igjen dyrkes et fotoresistmateriale over hele metallet og eksponerer UV-lyset gjennom mask4 som er etset for å danne den nødvendige sammenkoblingsdesignen. Den endelige PMOS-strukturen er vist nedenfor.

PMOS-transistoregenskaper

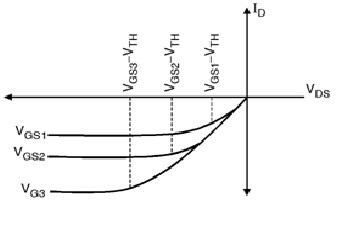

PMOS-transistor I-V-karakteristikkene er vist nedenfor. Disse karakteristikkene er delt inn i to regioner for å oppnå forholdet mellom avløpet til kildestrømmen (I DS) så vel som dens terminalspenninger som lineære og metningsområder.

I en liner-region vil IDS-en lineært øke når VDS (drain to source-spenning) økes, mens I DS i metningsområdet er stabil og uavhengig av VDS. Hovedforholdet mellom ISD (kilde til tappestrøm) og terminalspenningene er utledet av en lignende prosedyre for NMOS-transistoren. I dette tilfellet vil den eneste endringen være at ladningsbærerne som er tilstede i inversjonslaget ganske enkelt er hull. Når hullene beveger seg fra kilde til avløp, er strømflyten også den samme.

Dermed vises det negative tegnet innenfor den gjeldende ligningen. I tillegg er alle påførte forspenninger ved terminalene til enheten negative. Så PMOS-transistorens ID - VDS-karakteristikk er vist nedenfor.

Dreneringsstrømligningen for PMOS-transistoren i det lineære området er gitt som:

ID = – mp Cox

På samme måte er Drain-strømligningen for PMOS-transistor i metningsområdet gitt som:

ID = – mp Cox (VSG – | V TH |p )^2

Der 'mp' er hullets mobilitet og '|VTH| p' er PMOS-transistorens terskelspenning.

I ligningen ovenfor vil det negative tegnet indikere at ID( tappe strøm ) strømmer fra avløpet (D) til kilden (S), mens hull strømmer i motsatt retning. Når mobiliteten til hullet er lav sammenlignet med elektronmobiliteten, lider PMOS-transistorer av evnen til lavstrømsdriften.

Dermed handler dette om en oversikt over PMOS-transistor eller p-type mos-transistor - fabrikasjon, krets og dens virkemåte. PMOS transistorer er designet med en p-kilde, et n-substrat og avløp. Ladningsbærerne til PMOS er hull. Denne transistoren leder når lav spenning påføres ved portterminalen. PMOS-baserte enheter er mindre utsatt for forstyrrelser sammenlignet med NMOS-enheter. Disse transistorene kan brukes som spenningsstyrte motstander, aktive laster, strømspeil, transimpedansforsterkere, og også brukes i brytere og spenningsforsterkere. Her er et spørsmål til deg, hva er en NMOS-transistor?