I dette innlegget vil vi lære hvordan du bygger NOT, AND, NAND, OR og NOR logiske porter ved hjelp av diskrete transistorer. Hovedfordelen med å bruke transistorlogiske porter er at de kan fungere selv med spenninger så lave som 1,5 V.

I noen elektroniske applikasjoner kan den tilgjengelige spenningen være utilstrekkelig for å drive TTL eller til og med CMOS IC-er. Dette gjelder spesielt for dingser som går på batterier. Ingen tvil om at du alltid har 3-volts logisk IC-alternativ. Disse er imidlertid ikke alltid lett tilgjengelige for entusiasten eller eksperimentatoren, og de fungerer ikke under deres definerte spenningsspesifikasjoner (vanligvis under 2,5 volt DC).

Videre kan det bare være plass til et enkelt 1,5-volts batteri i en batteridrevet applikasjon. Vel, hva skal du gjøre da? Vanligvis IC logiske porter kan erstattes av transistoriserte logiske porter. For hver bestemt logisk port kreves vanligvis bare et par transistorer, og for en typisk NOT-gate-inverterlogikk kreves det bare én transistor.

FET versus bipolar transistor

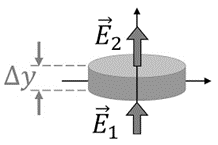

Felteffekttransistorer (FET) vs bipolare transistorer : hvilket er det bedre alternativet for lavspente logiske kretser? En flott egenskap ved FAKTA er at deres 'på' motstand er utrolig lav. I tillegg trenger de svært lav gate-turn-on strøm.

Imidlertid har de én begrensning i ekstremt lavspenningsapplikasjoner. Vanligvis er gatespenningsgrensen en volt eller så. Videre kan den tilgjengelige spenningen synke under FETens optimale arbeidsområde dersom en strømbegrensende eller nedtrekksmotstand er festet til porten.

Omvendt har bipolare svitsjetransistorer en fordel i ekstremt lavspente, enkeltbatteriapplikasjoner siden de bare trenger 0,6 til 0,7 volt for å slå på.

Dessuten er de fleste vanlige FET-er, som vanligvis selges i boblepakker hos din nærmeste elektronikkbutikk, ofte dyrere enn bipolare transistorer. Dessuten kan en bulkpakke med bipolare transistorer generelt kjøpes for prisen av et par FET-er.

FET-håndtering krever betydelig mer forsiktighet enn bipolar transistorhåndtering. Elektrostatisk og generell eksperimentell misbruk gjør FET-er spesielt utsatt for skade. Brente komponenter kan ødelegge en hyggelig, kreativ kveld med eksperimentering eller innovasjon, for ikke å glemme den følelsesmessige smerten ved feilsøking.

Grunnleggende om å bytte transistorer

Eksemplene på logiske kretser som er forklart i denne artikkelen, bruker bipolare NPN-transistorer siden de er rimelige og ikke trenger spesiell håndtering. For å unngå å skade enheten eller delene som støtter den, bør passende sikkerhetstiltak iverksettes før du kobler til kretsen.

Selv om kretsene våre hovedsakelig er sentrert om bipolare koblingstransistorer (BJT), kunne de like godt ha blitt konstruert ved hjelp av FET-teknologi.

Den grunnleggende bryterkretsen er en enkel transistorapplikasjon, som er en av de enkleste designene.

Å lage en NOT-port med en enkelt transistor

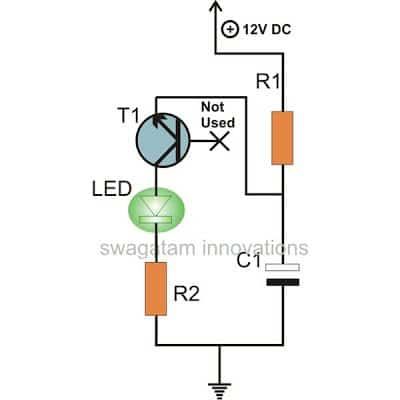

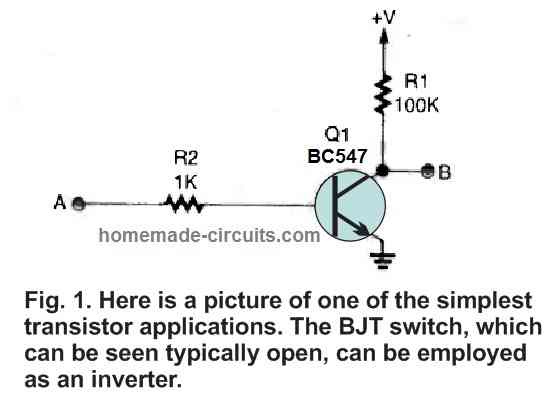

Et skjema av transistorbryteren er vist i figur 1. Avhengig av hvordan den er implementert i en bestemt applikasjon, kan bryteren ses som enten holdt lav eller normalt åpen.

En enkel NOT-gate-inverterlogikkport kan opprettes av den enkle svitsjekretsen vist i fig. 1 (hvor punkt A er inngangen). En NOT-port fungerer på en slik måte at hvis det ikke tilføres DC-forspenning til transistorens base (punkt A; Q1), vil den forbli avstengt, noe som resulterer i en høy eller logisk 1 (lik V+-nivå) ved utgangen ( punkt B).

Imidlertid aktiveres transistoren når den riktige forspenningen er gitt til basen av Q1, og skyver kretsens utgang lavt eller til logisk 0 (nesten lik null potensial). Transistoren, betegnet Q1, er en generell bipolar transistor, eller en BC547, som vanligvis brukes i laveffektsvitsje- og forsterkerapplikasjoner.

Enhver transistor som tilsvarer det (som 2N2222, 2N4401, etc.) vil fungere. R1 og R2s verdier ble valgt for å finne et kompromiss mellom lavt strømforbruk og kompatibilitet. I alle designene er motstandene alle 1/4 watt, 5 % enheter.

Forsyningsspenningen er justerbar mellom 1,4 og 6 volt DC. Legg merke til at kretsen kan fungere som en buffer når lastmotstanden og utgangsforbindelsen forskyves til transistorens emitter.

Å lage en bufferport ved å bruke en enkelt BC547 BJT

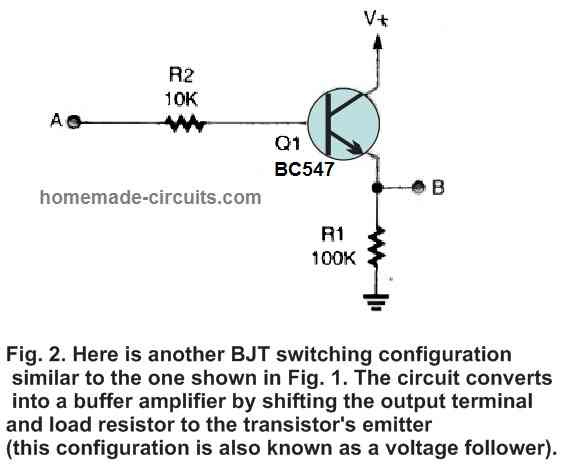

En spenningsfølger, eller bufferforsterker, er en type logisk svitsjkonfigurasjon som er identisk med den som er vist i figur 2. Det skal bemerkes at belastningsmotstanden og utgangsterminalen har blitt forskjøvet fra transistorens kollektor til emitteren i denne kretsen, som er den primære forskjellen mellom denne utformingen og den som er vist i fig. 1.

Transistorens funksjon kan også 'snus' ved å flytte belastningsmotstanden og utgangsterminalen til den andre enden av BJT.

Med andre ord, når ingen forspenning er gitt til kretsens inngang, forblir utgangen fra kretsen lav; men når en forspenning av tilstrekkelig spenning tilføres kretsens inngang, blir utgangen fra kretsen høy. (Det er nøyaktig det motsatte av hva som skjer i den tidligere kretsen.)

Utforming av logiske porter med to innganger ved bruk av transistorer

OG Gate ved hjelp av to transistorer

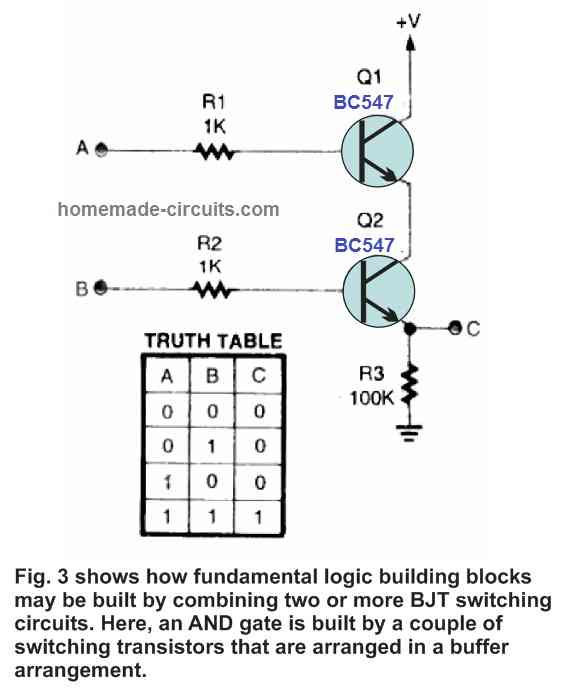

Figur 3 illustrerer hvordan en grunnleggende OG-port med to innganger kan opprettes ved å bruke et par buffere, sammen med sannhetstabellen for den porten. Sannhetstabellen illustrerer hva utdataresultatene vil være for hvert enkelt sett med innganger. Punktene A og B brukes som kretsens innganger, og punkt C fungerer som kretsens utgang.

Det er viktig å merke seg fra sannhetstabellen at bare ett sett med inngangsparametere resulterer i et logisk-høyt utgangssignal, mens alle andre inngangskombinasjoner resulterer i en logisk-lav utgang. Utgangen fra OG-porten i figur 3 forblir litt under V+ når den blir høy.

Dette skjer på grunn av spenningsfallet mellom de to transistorene (Q1 og Q2).

NAND-port som bruker to transistorer

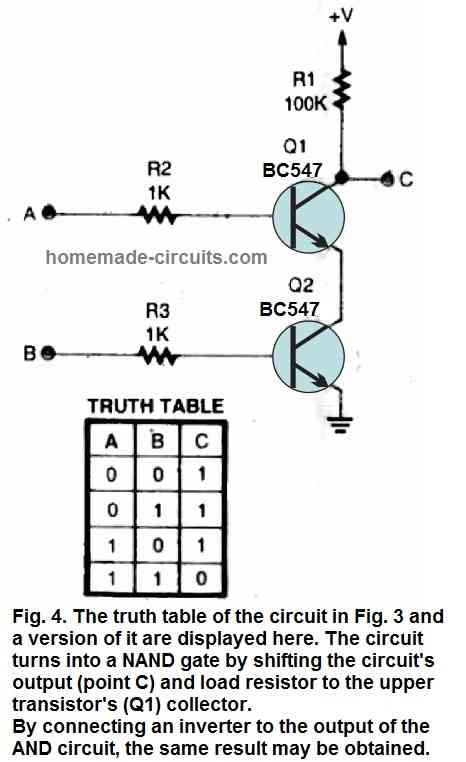

En annen variant av kretsen i figur 3 og tilhørende sannhetstabell er vist i figur 4. Kretsen blir til en NAND-port ved å forskyve utgangen (punkt C) og utgangsmotstanden til den øvre transistorens (Q1) kollektor.

Siden både Q1 og Q2 må slås PÅ for å trekke den lave siden av R1 til jord, er spenningstapet ved utgang C ubetydelig.

Hvis transistoren OG- eller transistorens NAND-porter trenger mer enn to innganger, kan flere transistorer godt kobles til i de viste designene for å gi tre, fire osv. inngangs- OG- eller NAND-porter.

Men for å kompensere for spenningstapene til de enkelte transistorene bør V+ økes tilsvarende.

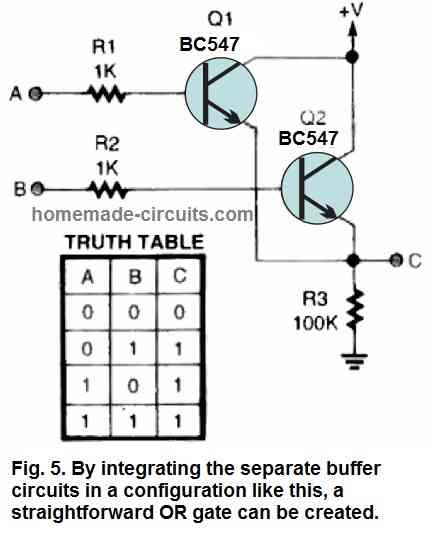

ELLER Gate som bruker to transistorer

En annen form for logisk krets med to innganger kan sees i figur 5, sammen med ELLER-portkretsens sannhetstabell.

Utgangen til kretsen er høy når enten inngang A eller inngang B presses høyt, men på grunn av kaskadetransistorene er spenningsfallet over 0,5 volt. Nok en gang indikerer tallene som vises at det er nok spenning og strøm til å betjene den påfølgende transistorporten.

NOR-port som bruker to transistorer

Figur 6 viser neste port på listen vår, en NOR-port med to innganger, sammen med sannhetstabellen. I likhet med hvordan OG- og NAND-porter reagerer på hverandre, gjør OR- og NOR-kretser det samme.

Hver av portene som vises er i stand til å levere nok drivkraft til å aktivere minst én eller flere tilstøtende transistorporter.

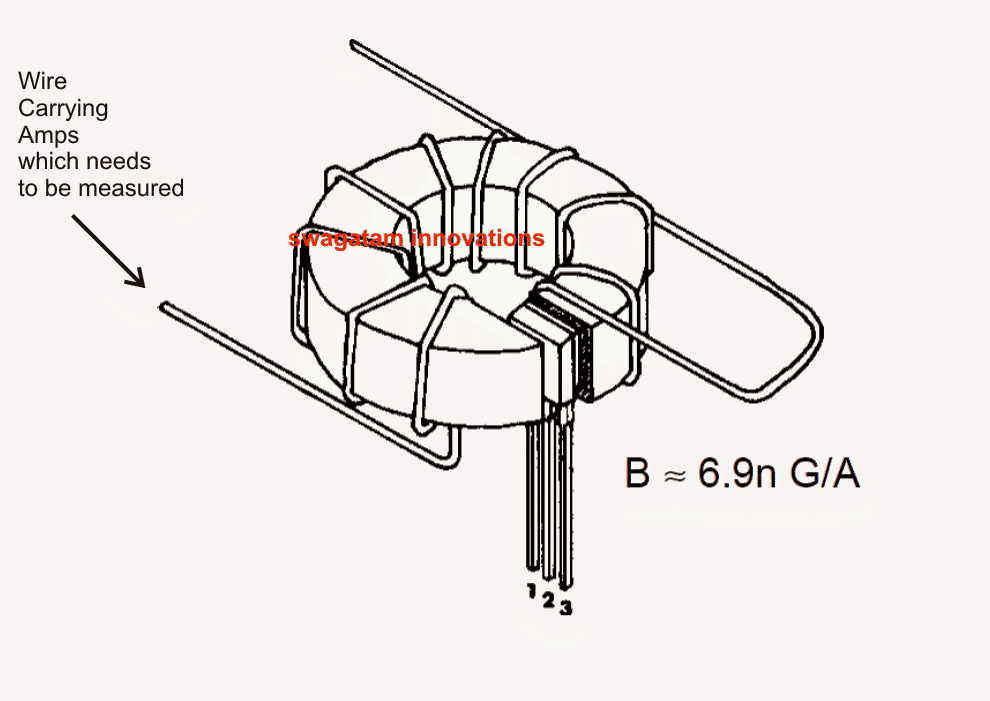

Transistor Logic Gate-applikasjoner

Hva gjør du med de ovenfor forklarte digitale kretsene som du nå har? Alt du kan oppnå med konvensjonelle TTL- eller CMOS-porter, men uten å bekymre deg for forsyningsspenningsbegrensningene. Her er noen få anvendelser av transistor-logiske porter i aksjon.

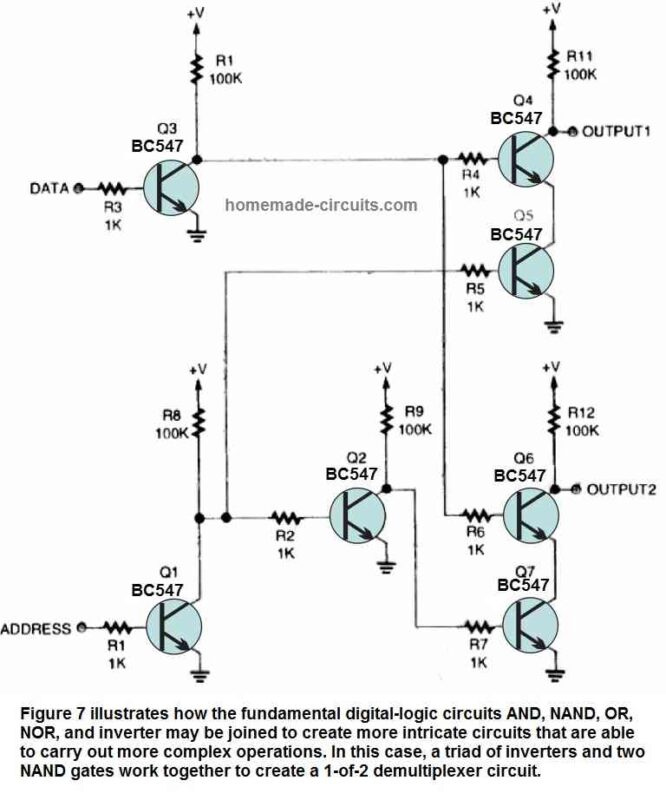

Demultiplekserkrets

En 1-av-2 demultiplekser med tre IKKE-porter og to NAND-kretser er vist i figur 7. Den passende utgangen velges ved å bruke en-bits 'adresseinngang', som kan være enten OUTPUT1 eller OUTPUT2, mens kjøreinformasjonen brukes til kretsen ved hjelp av DATA-inngangen.

Kretsen fungerer mest effektivt når datahastigheten holdes under 10 kHz. Kretsens funksjonalitet er grei. DATA-inngangen leveres med det nødvendige signalet, som slår PÅ Q3 og inverterer innkommende data ved Q3s samler.

Utgangen fra Q1 blir drevet høy hvis ADRESSE-inngangen er lav (jordet eller ikke gitt noe signal). Ved Q1s kollektor er høyeffekten delt inn i to baner. I den første banen tilføres Q1s utgang til Q5s base (en av benene til en NAND-port med to innganger), slår den på og 'aktiverer' derfor NAND-porten som består av Q4 og Q5.

I den andre banen tilføres Q1s høye utgang samtidig til inngangen til en annen IKKE-port (Q2). Etter å ha gjennomgått en dobbel inversjon, blir Q2s utgang lav. Denne lave tilføres Q7s base (en terminal på en andre NAND-port, som består av Q6 og Q7), og slår dermed av NAND-kretsen.

All informasjon eller signal som tilføres DATA-inngangen kommer til OUTPUT1 under disse omstendighetene. Alternativt reverseres situasjonen hvis det gis et høyt signal til ADRESSE-inngangen. Det betyr at all informasjon gitt til kretsen vil vises ved OUTPUT2 siden Q4/Q5 NAND-porten er deaktivert og Q6/Q7 NAND-porten er aktivert.

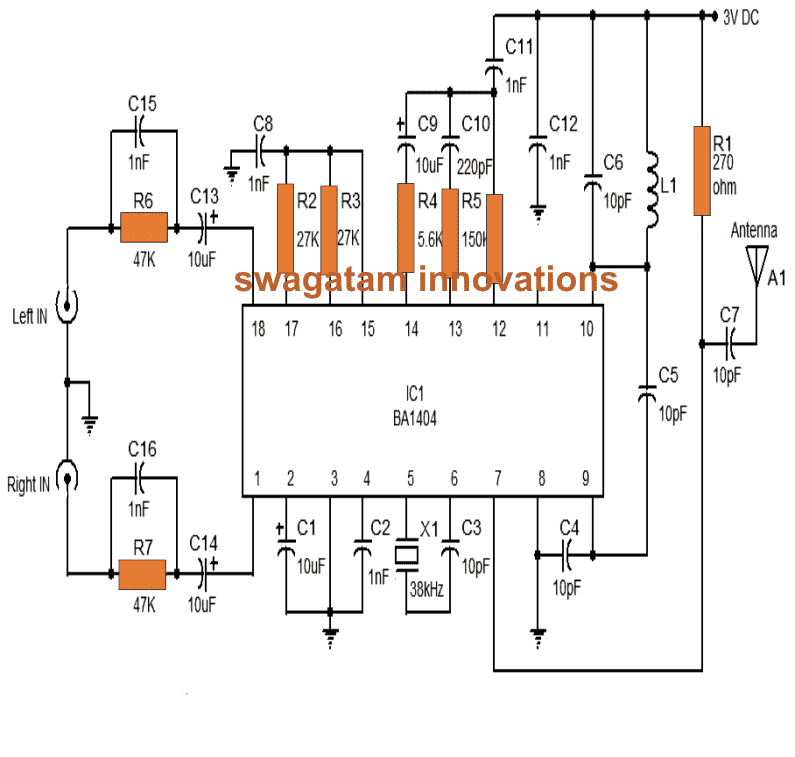

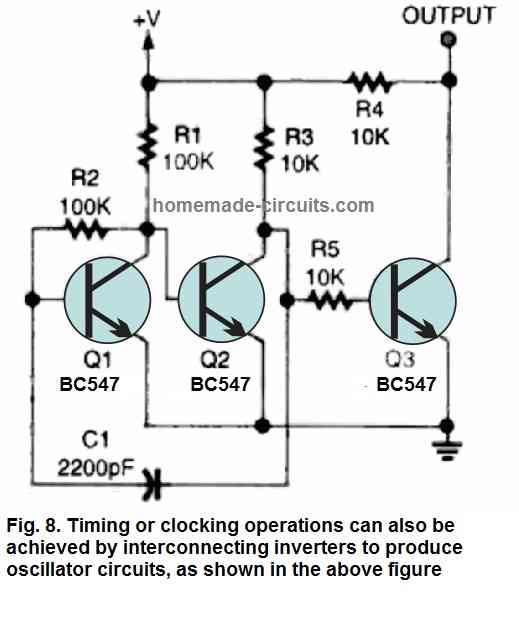

Oscillatorkrets (klokkegenerator)

Vår neste transistor logiske gate-applikasjon, illustrert i fig. 8, er en grunnleggende klokkegenerator (også kjent som en oscillator) laget av tre vanlige NOT-gate-invertere (hvorav den ene er forspent ved hjelp av en tilbakekoblingsmotstand, R2, som setter den inn i den analoge regionen).

For å avvikle utgangen er en tredje IKKE-port (Q3) som leverer komplementet til oscillatorutgangen inkludert. C1-verdien kan økes eller reduseres for å endre kretsens driftsfrekvens. Utgangsbølgeformen har en frekvens på rundt 7 kHz med V+ ved 1,5 volt DC, ved å bruke de angitte komponentverdiene.

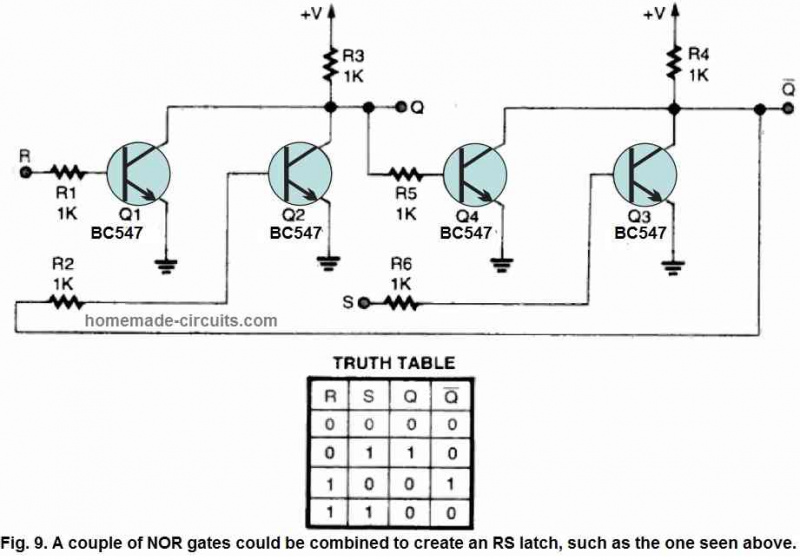

RS låsekrets

Fig. 9 viser vår endelige applikasjonskrets, en RS-lås som består av to NOR-porter. For å sikre en sunn utgangsdrift ved Q- og Q-utgangene, er motstandene R3 og R4 justert til 1k ohm.

RS-låsens sannhetstabell vises sammen med den skjematiske utformingen. Dette er bare noen få illustrasjoner av de mange pålitelige, lavspente, digitale, logiske portkretsene som kan lages ved hjelp av individuelle transistorer.

Kretser som bruker transistorisert logikk trenger for mange deler

Mange problemer kan løses ved å bruke alle disse lavspente transistoriserte logiske kretsene. Å bruke for mange av disse transistoriserte portene kan imidlertid føre til nye problemer.

Antallet transistorer og motstander kan bli ganske stort hvis applikasjonen du bygger inneholder en stor mengde porter som opptar verdifull plass.

Å bruke transistorarrays (mange transistorer innelukket i plast) og SIP (Single Inline Package) motstander i stedet for individuelle enheter er en måte å løse dette problemet på.

Tilnærmingen ovenfor kan spare tonn plass på et kretskort samtidig som ytelsen opprettholdes lik ytelsen til deres ekvivalenter i full størrelse. Transistor-arrays tilbys i overflatemontert emballasje, 14-pinners gjennomgående hull og firkantet emballasje.

For de fleste kretser kan blandingstransistortyper være ganske akseptable.

Ikke desto mindre er det tilrådelig at eksperimentatoren arbeider med en enkelt type transistor for å bygge de transistoriserte logiske kretsene (som betyr at hvis du lager en seksjon av en port ved å bruke BC547, så prøv å bruke den samme BJT for å lage de andre gjenværende portene også).

Begrunnelsen er at ulike transistorvarianter kan ha noe forskjellige egenskaper og dermed kan oppføre seg annerledes.

For noen transistorer kan for eksempel baseinnkoblingsgrensen være større eller mindre enn en annen, eller man kan ha en samlet strømforsterkning som er litt høyere eller lavere.

På den annen side kan kostnadene ved å kjøpe en bulkboks av en enkelt type transistor også være lavere. Ytelsen til kretsene dine vil forbedres hvis de logiske portene dine bygges ved hjelp av matchende transistorer, og prosjektet i sin helhet vil bli mer givende til slutt.