Generelt kan et register defineres som en enhet som brukes til å lagre binære data, men hvis du vil lagre flere databiter, brukes et sett med flip flops som er koblet i serie. Dataene som er lagret i registrene kan forskyves ved å bruke skiftregistre på enten høyre eller venstre side ved å gi CLK-pulser. Skiftregister er en gruppe av flip flops brukes til å lagre flere databiter. På samme måte kan et skiftregister med n-biter dannes ved ganske enkelt å koble til n flip-flops der hver flip-flop ganske enkelt lagrer en enkelt databit. Når registeret flytter bitene til høyre side, er det høyre skiftregister, mens hvis det skifter til venstre side, er det kjent som et venstre skiftregister. Denne artikkelen diskuterer en oversikt over en av typene skiftregister, nemlig seriell i parallell ut skiftregister eller SIPO skiftregister .

Hva er SIPO Skiftregister?

Skiftregisteret som tillater seriell inngangs parallell utgang er kjent som SIPO-skiftregisteret. I SIPO-registeret står begrepet SIPO for seriell inngangs parallell utgang. I denne typen skiftregister blir inngangsdataene gitt bit for bit serielt. For hver klokkepuls kan inngangsdataene ved alle FF-ene forskyves med en enkelt posisjon. O/p på hver flip-flop kan mottas parallelt.

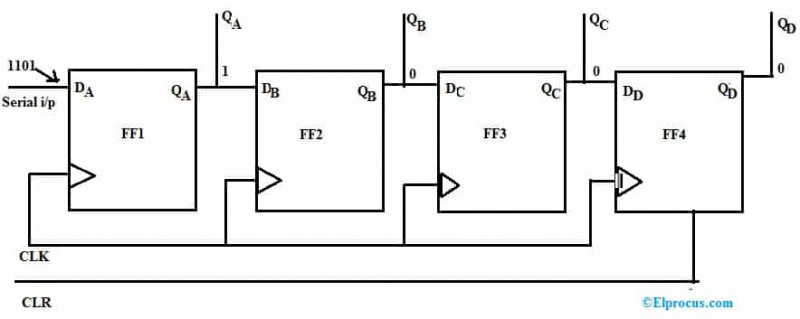

Kretsdiagram

De SISO skiftregister kretsskjema er vist nedenfor. Denne kretsen kan bygges med 4 D flip-flops som kobles til som vist i diagrammet hvor CLR-signalet gis i tillegg til CLK-signalet til alle FF-er eller RESET dem. I kretsen ovenfor gis den første FF-utgangen til den andre FF-inngangen. Alle disse fire D-flip-floppene er forbundet med hverandre i serie fordi det samme CLK-signalet gis til hver flip-flop.

Arbeid av SIPO Skiftregister

Arbeidet til SIPO-skiftregisteret er; at den tar den serielle datainngangen fra den første flip-flop på venstre side og genererer en parallell datautgang. 4-bit SIPO skiftregisterkretsen er vist nedenfor. Operasjonen til dette skiftregisteret er, først må alle flip-floppene fra kretsen fra FF1 til FF4 RESETTE slik at alle utgangene til FF-er som QA til QD vil være på logisk null-nivå slik at det ikke er noen parallell datautgang.

Oppbyggingen av SIPO-skiftregisteret er vist ovenfor. I diagrammet er den første flip-flop-utgangen 'QA' koblet til den andre flip-flop-inngangen 'DB'. Den andre flip-flops-utgangen 'QB' er koblet til den tredje flip-flops-inngangen DC, og den tredje flip-flops-utgangen 'QC' er koblet til den fjerde flip-flops-inngangen 'DD. Her er QA, QB, QC og QD datautganger.

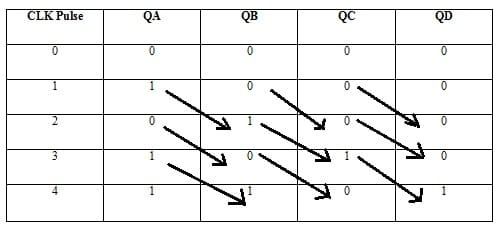

Til å begynne med vil all utgang bli null, så uten CLK-puls; alle data blir null. La oss ta et eksempel på 4-bits datainndata som 1101. Hvis vi påfører den første klokkepulsen '1' på den første flip-flop, blir dataene som skal legges inn i FF og QA '1', og gjenværende alle utganger som QB , QC og QD blir null. Så den første datautgangen er '1000'

Hvis vi bruker den andre klokkepulsen som '0' på den første flip-flop, blir QA '0', QB blir '0', QC blir '0' og QD blir '0'. Så den andre datautgangen blir '0100' på grunn av høyreskiftprosessen.

Hvis vi bruker den tredje klokkepulsen som '1' på den første flip-flop, blir QA '1', QB blir '0', QC blir '1' og QD blir '0'. Så den tredje datautgangen blir '1011' på grunn av høyreskiftprosessen.

Hvis vi bruker den fjerde klokkepulsen som '1' på den første flip-flop, så blir QA '1', QB blir '1', QC blir '0' og QD blir '1'. Så den tredje datautgangen blir '1101' på grunn av høyreskiftprosessen.

SIPO Shift Register Sannhetstabell

Sannhetstabellen til SIPO-skiftregisteret er vist nedenfor.

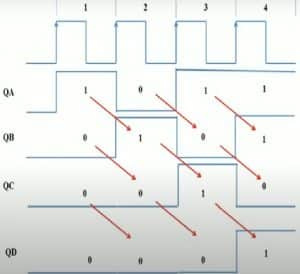

Tidsdiagram

De tidsdiagram for SIPO-skiftregisteret er vist nedenfor.

Her bruker vi et CLK i/p-signal med positiv kant. I en første klokkepuls blir inngangsdataene QA = '1' og alle andre verdier som QB, QC og QD blir '0'. Så utgangen blir '1000'. I den andre klokkepulsen vil utgangen bli '0101'. I den tredje klokkepulsen vil utgangen bli '1010' og i den fjerde klokkepulsen vil utgangen bli '1101'.

SIPO Shift Register Verilog Code

Verilog-koden for SIPO-skiftregisteret er vist nedenfor.

modul sipomod(clk,clear, si, po);

input clk, si, clear;

utgang [3:0] po;

reg [3:0] tmp;

reg [3:0] po;

alltid @(posedge clk)

begynne

hvis (klart)

tmp <= 4'b0000;

ellers

tmp <= tmp << 1;

tmp[0] <= ja;

po = tmp;

slutt

endemodul

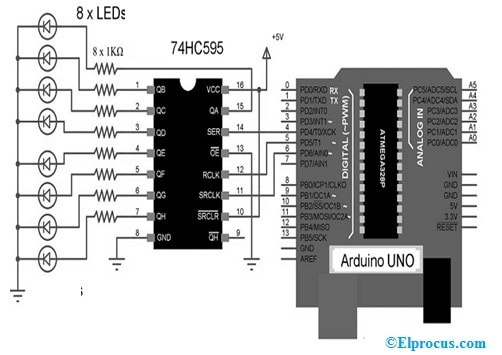

74HC595 IC SIPO skiftregisterkrets og dens funksjon

En 74HC595 IC er et 8-bits seriell i parallell ut skiftregister, så den bruker innganger serielt og gir parallelle utganger. Denne IC inkluderer 16-pinner og er tilgjengelig i forskjellige pakker som SOIC, DIP, TSSOP og SSOP.

Pinkonfigurasjonen til 74HC595 er vist nedenfor der hver pinne er diskutert nedenfor.

Pinne 1 til 7 og 15 (QB til QH & QA): Dette er o/p-pinnene som brukes til å koble til utgangsenheter som 7-segments skjermer og lysdioder.

Pin8 (GND): Denne GND-pinnen kobles ganske enkelt til GND-pinnen til strømforsyningen til mikrokontrolleren.

Pin9 (QH): Denne pinnen brukes til å koble til SER-pinnen til en annen IC og gi samme CLK-signal til begge IC-ene slik at de fungerer som en enkelt IC inkludert 16-utganger.

Pin16 (Vcc): Denne pinnen brukes til å koble til mikrokontrolleren ellers Strømforsyning fordi det er en 5V logisk nivå IC.

Pin14 (BE): Det er den serielle i/p-pinnen hvor dataene legges inn serielt gjennom denne pinnen.

Pin11 (SRCLK): Det er Shift Register CLK Pin som fungerer som CLK for Shift Register fordi CLK signalet er gitt gjennom hele denne pin.

Pin12 (RCLK): Det er Register CLK-pinnen som brukes til å observere o/ps på enhetene som er koblet til disse IC-ene.

Pin10 (SRLR): Det er Shift Register CLR Pin. Denne pinnen brukes hovedsakelig når vi trenger å tømme registerets lagring.

Pin13 (OE): Det er o/p Enable Pin. Når denne pinnen er satt til HØY, blir skiftregisteret satt til en tilstand med høy impedans og o/ps blir ikke overført. Hvis vi setter denne pinnen til lav, kan vi få o/ps.

74HC595 IC Fungerer

Kretsskjemaet til 74HC595 IC for styring av lysdioder er vist nedenfor. De 3-pinnene til skiftregisteret er nødvendig for å kobles til Arduino som pinnene 11, 12 og 14. Alle de åtte LED-ene vil ganske enkelt kobles til denne skiftregister-IC.

De nødvendige komponentene for å designe denne kretsen inkluderer hovedsakelig en 74HC595 Shift Register IC, Arduino UNO, 5V strømforsyning, Breadboard, 8 LED-er, 1KΩ motstander – 8, og tilkoblingsledninger.

Først må den serielle i/p-pinnen til Shift-registeret kobles til Pin-4 til Arduino Uno. Deretter kobler du både CLK- og låsepinnene som pinnene 11 og 12 på IC til henholdsvis pinnene 5 og 6 på Arduino Uno. Lysdiodene kobles til ved å bruke 1KΩ strømbegrensningsmotstander til 8-o/p pinnene til IC. En separat 5V strømforsyning brukes for 74HC595 IC med felles GND til Arduino før 5V tilføres fra Arduino.

Kode

Den enkle koden for å aktivere 8 lysdioder PÅ i en serie er vist nedenfor.

int latchPin = 5;

int clkPin = 6;

int dataPin = 4;

byte LED = 0;

ugyldig oppsett()

{

Serial.begin(9600);

pinMode(latchPin, OUTPUT);

pinMode(dataPin, OUTPUT);

pinMode(clkPin, OUTPUT);

}

void loop()

{

int i=0;

LED = 0;

shiftLED();

forsinkelse(500);

for (i = 0; i < 8; i++)

{

bitSet(LED, i);

Serial.println(LED);

shiftLED();

forsinkelse(500);

}

}

void shiftLED()

{

digitalWrite(latchPin, LOW);

shiftOut(dataPin, clkPin, MSBFIRST, LED);

digitalWrite(latchPin, HIGH);

}

Virkemåten til denne skiftregisterkretsen er at først vil alle de 8 lysdiodene bli slått AV fordi bytevariabelen lysdioden er satt til null. Nå er hver bit satt til 1 med 'bitSet'-funksjonen og flyttes ut med 'shiftOut'-funksjonen. På samme måte vil hver LED slås PÅ i samme serie. Hvis du vil slå av LED-en, kan du bruke 'bitClear'-funksjonen.

74HC595 Shift Register IC brukes i forskjellige applikasjoner som servere, LED-kontroll, industriell kontroll, elektroniske apparater, nettverkssvitsjer, etc.

applikasjoner

De applikasjoner av serieinngang parallell utgang skiftregister er vist nedenfor.

- Vanligvis brukes skiftregisteret til å lagre midlertidige data, brukt som en ring & Johnson Ringeteller .

- Disse brukes til overføring av data og manipulasjon.

- Disse flip-floppene brukes hovedsakelig innenfor kommunikasjonslinjer der det er nødvendig med en datalinje som demultiplekser til flere parallelle linjer fordi dette skiftregisteret brukes til å endre dataene fra seriell til parallell.

- Disse brukes til datakryptering og dekryptering.

- Dette skiftregisteret brukes i CDMA for å generere PN-kode eller Pseudo-støysekvensnummer.

- Vi kan bruke dem til å spore dataene våre!

- SIPO-skiftregisteret brukes i ulike digitale applikasjoner for datakonvertering.

- Noen ganger kobles denne typen skiftregister ganske enkelt til mikroprosessoren når flere GPIO-pinner er nødvendige.

- Den praktiske anvendelsen av dette SIPO-skiftregisteret er å gi mikroprosessorens utdata til en ekstern panelindikator.

Dermed er dette en oversikt over SIPO skiftregister – krets, arbeids-, sannhetstabell og tidsdiagram med applikasjoner. De mest brukte SIPO-skiftregisterkomponentene er 74HC595, 74LS164, 74HC164/74164, SN74ALS164A, SN74AHC594, SN74AHC595 og CD4094. Disse registrene er svært raske i bruk, dataene kan konverteres veldig enkelt fra seriell til parallell, og designet er enkelt. Her er et spørsmål til deg, hva er PISO-vaktregisteret.