JTAG (Joint Test Action Group) er en veletablert IEEE 1149.1-standard som ble utviklet i år 1980 for å løse produksjonsproblemene som oppstod innen elektroniske tavler eller trykte kretskort . Denne teknologien brukes til å gi nok testtilgang for hvert komplekst bord når testtilgangen var redusert. Dermed ble grenseskanningsteknologien lansert og JTAG-standarden eller JTAG-spesifikasjon er etablert. Kompleksiteten til elektronikk har økt dag for dag, så JTAG-spesifikasjonen har blitt det aksepterte testformatet for å teste kompliserte og kompakte elektronikkenheter. Denne artikkelen diskuterer en oversikt over en JTAG protokoll – arbeid med applikasjoner.

Hva er JTAG?

Navnet som er gitt til IEEE 1149.1 Standard Test Access Port samt Boundary-Scan Architecture er kjent som JTAG (Joint Test Action Group). Denne grenseskanningsarkitekturen brukes mest i datamaskiner prosessorer fordi den første prosessoren med JTAG ble utgitt av Intel. Denne IEEE-standarden definerer ganske enkelt hvordan kretsen til en datamaskin testes for å bekrefte om den fungerer som den skal etter produksjonsprosedyren. På kretskortene utføres tester for å kontrollere loddeforbindelsene.

Joint Test Action Group gir en pin-out-visning for testere med hver IC-pute som hjelper til med å identifisere eventuelle feil på et kretskort. Når denne protokollen er koblet til en brikke, kan denne feste en sonde til brikken ved å la en utvikler kontrollere brikken så vel som dens forbindelser med andre brikker. Grensesnittet med Joint Test Action-gruppen kan også brukes av utviklere for å kopiere fastvaren til ikke-flyktig minne i en elektronisk enhet.

Konfigurasjon/Pin Out

Joint Test Action Group inkluderer 20-pinner hvor hver pinne og dens funksjon er diskutert nedenfor.

Pin1 (VTref): Dette er målreferansespenningspinnen som brukes til å koble til hovedstrømforsyningen til målet som varierer fra 1,5 til 5,0VDC.

Pin2 (Vsupply): Dette er målforsyningsspenningen som brukes til å koble til hovedspenningsforsyningen til mål 1,5VDC – 5,0VDC.

Pin3 (nTRST): Dette er en testtilbakestillingspinne som brukes til å tilbakestille tilstandsmaskinen til TAP-kontrolleren.

Pinner (4, 6, 8, 10, 12, 14, 16, 18 og 20): Dette er vanlige GND-pinner.

Pin5 (TDI): Dette er testdata i pinnen. Disse dataene flyttes til målenheten. Denne pinnen må trekkes opp på en definert tilstand på målbrettet.

Pin7 (TMS): Dette er testmodustilstandspinnen som trekkes for å bestemme den neste tilstanden til tilstandsmaskinen til TAP-kontrolleren.

Pin9 (TCK): Dette er en testklokkepinne som synkroniserer de interne tilstandsmaskinoperasjonene i TAP-kontrolleren.

Pin11 (RTCK): Dette er Input Return TCK-pinnen som brukes i enheter som støtter adaptiv klokke.

Pin13 (TDO): Dette er Test Data Out-pinnen, slik at dataene flyttes ut av målenheten og inn i Flueswatter.

Pin15 (nSRST): Dette er tilbakestillingspinnen for målsystem som er koblet til målets hovedtilbakestillingssignal.

Pinner 17 og 19 (NC): Disse er ikke tilkoblede pinner.

JTAG fungerer

JTAGs opprinnelige bruk er for grensetesting. Her er et enkelt trykt kretskort inkludert to IC-er som CPU og FPGA . Et typisk kort kan inneholde mange IC-er. Generelt inkluderer IC-er mange pinner som er koblet sammen med mange tilkoblinger. Her, i følgende diagram, er bare fire tilkoblinger vist.

Så hvis du designer mange brett der hvert brett har tusenvis av tilkoblinger. I det er det noen dårlige brett. Så vi må sjekke hvilket styre som fungerer og hvilket som ikke fungerer. For det ble Joint Test Action Group designet.

Denne protokollen kan bruke kontrollpinnene til alle brikkene, men i det følgende diagrammet kommer Joint Test Action Group til å lage alle utgangspinnene til CPU-en og alle inngangspinnene til FPGA. Etter det, ved å overføre en viss mengde data fra pinnene til CPU-en og lese verdiene til pinnene fra FPGA, sier JTAG at tilkoblingene til PCB-kortet er fine.

Faktisk inkluderer Joint Test Action Group fire logiske signaler TDI, TDO, TMS og TCK. Og disse signalene må kobles sammen på en bestemt måte. Til å begynne med er TMS og TCK koblet parallelt til alle IC-ene til JTAG.

Etter det kobles både TDI og TDO sammen for å danne en kjede. Som du kan observere, inkluderer hver JTAG-kompatibel IC 4-pinner som brukes til JTAG der 3-pinner er innganger og fjerde pinne er utgang. Den femte pinnen som TRST er valgfri. Vanligvis deles ikke JTAG-pinnene til andre formål.

Ved å bruke Joint Test Action Group, bruker alle IC-er grensetesting som den opprinnelige årsaken er opprettet av JTAG. For tiden er bruken av denne protokollen utvidet til å tillate forskjellige ting som å konfigurere FPGA-er, og etter det brukes JTAG i FPGA-kjernen for feilsøkingsformål.

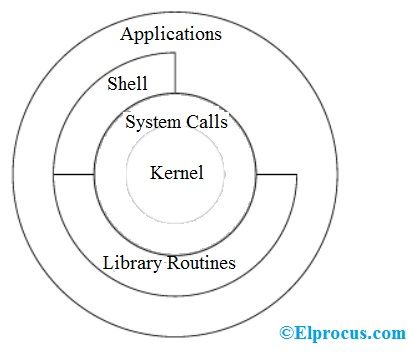

JTAG arkitektur

JTAG-arkitekturen er vist nedenfor. I denne arkitekturen blir alle signalene mellom kjernelogikken til enheten og pinnene avbrutt gjennom en seriell skannebane kalt BSR eller Boundary Scan Register. Denne BSR inkluderer forskjellige grenseskanningsceller. Generelt er disse grenseskanningscellene ikke synlige, men de kan brukes til å angi eller lese verdier i testmodus fra enhetens pinner.

JTAG-grensesnittet kalt en TAP eller Test Access Port bruker forskjellige signaler for å støtte grenseskanningsoperasjonen som TCK, TMS, TDI, TDO og TRST.

- TCK- eller testklokkesignalet synkroniserer ganske enkelt de indre operasjonene til en tilstandsmaskin.

- TMS eller Test Mode Select-signal samples ved den økende kanten av et testklokkesignal for å bestemme neste tilstand.

- TDI eller Test Data In-signal angir de forskjøvne dataene inn i testenheten ellers programmeringslogikk. Når den indre tilstandsmaskinen er i riktig tilstand, blir den samplet ved den økende kanten av TCK.

- TDO eller Test Data Out-signal angir de forskjøvne dataene til testenheten ellers programmeringslogikk. Når den indre tilstandsmaskinen er i riktig tilstand, er den gyldig på den avtagende kanten av TCK

- TRST eller Test Reset er en valgfri pinne som brukes til å tilbakestille tilstandsmaskinen til TAP-kontrolleren.

TAP-kontroller

Testtilgangspunktet i arkitekturen til JTAG er sammensatt av en TAP-kontroller, et instruksjonsregister og testdataregistre. Denne kontrolleren inkluderer teststatusmaskinen som er ansvarlig for å lese TMS- og TCK-signalene. Her brukes data i/p-pinnen ganske enkelt til å laste data inn i grensecellene mellom IC-kjernen og fysiske pinner, og også laste data inn i et av dataregistrene eller inn i instruksjonsregisteret. Data o/p pin brukes til å lese data fra enten registrene eller grensecellene.

Tilstandsmaskinen til TAP-kontrolleren styres av TMS og den klokkes av TCK. Tilstandsmaskin bruker to baner for å angi to forskjellige moduser som instruksjonsmodus og datamodus.

Registrerer

Det er to typer registre tilgjengelig innenfor grenseskanning. Hver kompatibel enhet inkluderer minst to eller flere dataregistre og ett instruksjonsregister.

Instruksjonsregister

Instruksjonsregisteret brukes til å holde gjeldende instruksjon. Så dataene deres brukes av TAP-kontrolleren til å bestemme hva som skal utføres med signaler som innhentes. Oftest vil instruksjonsregisterdata beskrive til hvilke av dataregistrene signaler må sendes.

Dataregistre

Dataregistrene er tilgjengelige i tre typer BSR (Boundary Scan Register), BYPASS & ID-KODE-registeret. Og også andre dataregistre kan være der, men de er ikke nødvendige som et element i JTAG-standarden.

Boundary Scan Register (BSR)

BSR er hovedtestdataregisteret som brukes til å flytte data fra og til enhetens I/O-pinner.

OMGANG

Bypass er et enkelt-bits register som brukes til å sende data fra TDI – TDO. Så det lar tilleggsenheter i en krets testes med minimum overhead.

ID-KODER

Denne typen dataregister inkluderer ID-koden samt revisjonsnummeret for enheten. Så disse dataene gjør at enheten kan kobles til BSDL-filen (Boundary Scan Description Language). Denne filen inkluderte Boundary Scan-konfigurasjonsdetaljene for enheten.

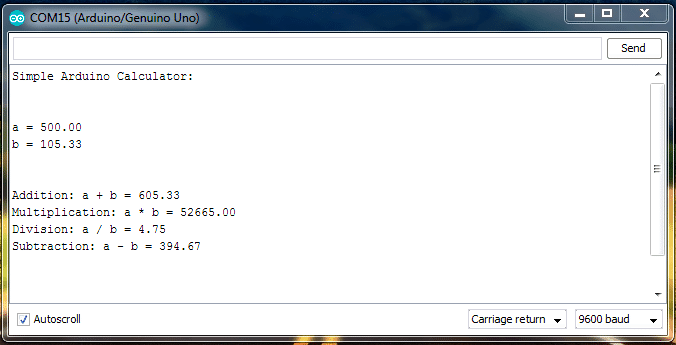

Virkemåten til JTAG er i utgangspunktet at instruksjonsmodusen velges der en av tilstandene i denne modusens 'bane' lar operatøren klokke innenfor en instruksjon fra TDI. Etter det utvikler statsmaskinen seg til den omorganiserer. Det neste trinnet for de fleste instruksjonene er å velge datamodus. Så i denne modusen lastes dataene gjennom TDI for å lese fra TDO. For TDI & TDO vil databanene bli arrangert i samsvar med instruksjonen som er klokket inn. Når lese/skriveoperasjonen er utført, utvikler tilstandsmaskinen igjen til tilbakestillingstilstanden.

Forskjellen mellom JTAG vs UART

Forskjellen mellom JTAG og UART inkluderer følgende.

| JTAG |

UART |

| Begrepet 'JTAG' står for Joint Test Action Group. | Begrepet ' UART ” står for Universal Asynchronous Receiver/Sender. |

| Det er et synkront grensesnitt som bruker innebygd maskinvare for å programmere blitsen . | UART er et asynkront grensesnitt som bruker en bootloader som kjører i minnet. |

| Det er et sett med testporter som brukes til feilsøking, men som også kan brukes til å programmere fastvare (som ofte gjøres).

|

UART er en type brikke som styrer kommunikasjon til og fra en enhet, for eksempel en mikrokontroller, ROM, RAM osv. Mesteparten av tiden er det en seriell forbindelse som lar oss kommunisere med en enhet. |

| Disse er tilgjengelige i fire typer TDI, TDO, TCK, TMS & TRST. | Disse er tilgjengelige i to typer dum UART & FIFO UART. |

| Joint Test Action Group er seriell programmering eller datatilgangsprotokoll som brukes i grensesnittet til mikrokontrollere og relaterte enheter. | En UART er en type brikke ellers mikrokontrollerens underkomponent som brukes til å gi maskinvaren for å generere en asynkron seriell strøm som RS-232/RS-485. |

| JTAG-komponenter er prosessorer, FPGA-er, CPLD-er , etc. | UART-komponenter er CLK-generator, I/O-skiftregistre, sende- eller mottaksbuffere, systemdatabussbuffer, lese- eller skrivekontrolllogikk, etc. |

JTAG Protocol Analyzer

JTAG Protocol Analyzer som PGY-JTAG-EX-PD er en type Protocol Analyzer inkludert noen funksjoner for å fange opp og feilsøke kommunikasjon mellom vert og design som testes. Denne typen analysator er det ledende instrumentet som lar test- og designingeniørene teste de spesielle designene til JTAG for spesifikasjonene ved å arrangere PGY-JTAG-EX-PD som Master eller Slave for å generere JTAG-trafikk og dekode dekodepakkene til Joint Test Action Group-protokoll.

Funksjoner

Funksjonene til JTAG-protokollanalysatoren inkluderer følgende.

- Den støtter opptil 25MH med JTAG-frekvenser.

- Den genererer JTAG-trafikk og protokolldekoder for bussen samtidig.

- Den har JTAG Master Capability.

- Variable JTAG-datahastigheter og driftssyklus.

- Brukerdefinerte TDI & TCK Delays.

- Vertsdatamaskin USB 2.0- eller 3.0-grensesnitt.

- Feilanalyse i Protocol Decode

- Protokolldekodet busstimingdiagram.

- Kontinuerlig protokolldatastrømming til vertsdatamaskinen for å gi en stor buffer.

- Protokollaktivitetsliste.

- Ved forskjellige hastigheter kan et øvelsesskript skrives for å kombinere generering av flere dataramme.

Tidsdiagram

De tidsdiagram for JTAG protokollen er vist nedenfor. I det følgende diagrammet forblir TDO-pinnen innenfor høyimpedanstilstanden bortsett fra under en skift-IR/skift-DR-kontrollertilstand.

I shift-IR- og Shift-DR-kontrollerforholdene oppdateres TDO-pinnen på den avtagende kanten av TCK gjennom Target og samplet på den økende kanten av TCK gjennom Host.

Både TDI- og TMS-pinnene er ganske enkelt samplet på den økende kanten av TCK gjennom Target. Oppdatert på avtagende kant ellers TCK gjennom Host.

applikasjoner

De JTAG-applikasjoner Inkluder følgende.

- Joint Test Action Group brukes ofte i prosessorer for å gi adgangsrett til deres emulerings- eller feilsøkingsfunksjoner.

- Alle CPLD-er og FPGA-er bruker dette som et grensesnitt for å gi tilgang til programmeringsfunksjonene deres.

- Den brukes til PCB-testing uten fysisk tilgang

- Den brukes til produksjonstester på brettnivå.

Altså handler dette om en oversikt over JTAG – pin-konfigurasjon, arbeid med applikasjoner. Bransjestandarden JTAG brukes til designverifisering samt PCB-testing etter produksjon. Her er et spørsmål til deg, JTAG står for?