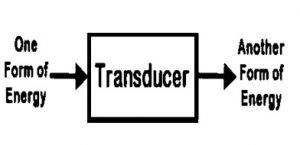

TIL digital-til-analog-omformer ( Dacian , D / A , D2A , eller D-til-A ) er en krets designet for å konvertere et digitalt inngangssignal til et analogt utgangssignal. Analog-til-digital-omformeren (ADC) fungerer på motsatt måte og forvandler et analogt inngangssignal til en digital utgang.

I denne artikkelen diskuterer vi hvordan digitale til analoge og analoge til digitale omformerkretser fungerer ved hjelp av diagrammer og formler.

I elektronikk kan vi finne spenninger og strømmer som varierer kontinuerlig med forskjellige områder og størrelser.

I digitale kretser er spenningssignalet i to former, enten som logiske høye eller logiske lave logiske nivåer, som representerer binære verdier på 1 eller 0.

I en analog til digital omformer (ADC) blir det analoge inngangssignalet representert som en digital størrelse, mens en digital-analog omformer (DAC) konverterer den digitale størrelsen tilbake til et analogt signal.

Hvordan fungerer digitale-til-analoge omformere

Digital-til-analog konverteringsprosess kan utføres gjennom mange forskjellige teknikker.

En velkjent metode bruker et nettverk av motstander, kjent som stigenettverk.

Et stigenettverk er designet for å akseptere innganger som involverer binære verdier, typisk ved 0 V eller Vref, og leverer en utgangsspenning som tilsvarer størrelsen på binærinngangen.

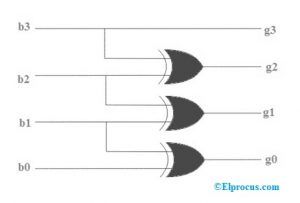

Figuren nedenfor viser et stigenettverk ved bruk av 4 inngangsspenninger, som representerer 4 biter med digitale data og en likestrømsutgang.

Utgangsspenningen er proporsjonal med den digitale inngangsverdien, uttrykt ved ligningen:

Å løse eksemplet ovenfor får vi følgende utgangsspenning:

Som vi ser, en digital inngang på 0110toblir konvertert til en analog utgang på 6 V.

Hensikten med stigenettverket er å endre de 16 potensielle binære størrelsene

gjennom 0000 til 1111 til en av de 16 spenningsmengdene med intervaller på V.ref/ 16.

Derfor kan det være mulig å behandle flere binære innganger ved å inkludere flere antall stigenheter, og å oppnå høyere kvantisering for hvert trinn.

Betydning, anta at hvis vi bruker et 10-trinns stigenettverk, vil det være mulig å øke spenningstrinnmengden eller oppløsningen til Vref/to10eller Vref/ 1024. I dette tilfellet, hvis vi brukte en referansespenning V.ref= 10 V vil generere utgangsspenning i trinn på 10 V / 1024, eller ved rundt 10 mV.

Dermed vil det å legge til flere trinn i trinn gi oss proporsjonalt høyere oppløsning.

Vanligvis for n antall trappetrinn, kan dette vises med følgende formel:

Vref/ ton

DAC-blokkskjema

Figuren nedenfor viser blokkdiagrammet til en standard DAC ved bruk av et stigenettverk, referert til som en R-2R-stige. Dette kan sees låst mellom referansestrømkilde og strømbrytere.

Strømbryterne er koblet til binære brytere, og produserer en utgangsstrøm proporsjonal med den inngående binære verdien.

De binære inngangene bytter mellom de respektive bena på stigen, og muliggjør en utgangsstrøm som er en vektet sum av gjeldende referanse.

Om nødvendig kan motstander festes med utgangene for å tolke resultatet som analog utgang.

Hvordan analog-til-digitale omformere fungerer

Så langt diskuterte vi hvordan man konverterer digitale til analoge signaler, la oss nå lære å gjøre det motsatte, det vil si å konvertere et analogt signal til et digitalt signal. Dette kan implementeres gjennom en velkjent metode kalt dual-helling metode .

Følgende figur viser blokkdiagrammet for standard ADC-omformer med dobbel helling.

Her brukes en elektronisk bryter for å overføre det ønskede analoge inngangssignalet til en integrator, også kalt en rampegenerator. Denne rampegeneratoren kan være i form av en kondensator ladet med en konstant strøm for å generere den lineære rampen. Dette produserer den nødvendige digitale konvertering gjennom et motstrinn som fungerer for både positive og negative stigningsintervaller for integratoren.

Metoden kan forstås med følgende beskrivelse:

Tellerens fulle måleområde bestemmer det faste tidsintervallet. For dette intervallet får den inngående analoge spenningen som påføres integratoren komparatorens inngangsspenning til å stige til noe positivt nivå.

Henviser til delen (b) i diagrammet ovenfor, viser at spenningen fra integratoren på slutten av det faste tidsintervallet er høyere enn inngangsspenningen som er større i størrelse.

Når det faste tidsintervallet er ferdig, er tellingen satt til 0, som ber den elektroniske bryteren om å koble integratoren til et fast referanseinngangsspenningsnivå. Etter dette begynner utgangen fra integratoren, som også er inngangen til kondensatoren, med en konstant hastighet.

I løpet av denne perioden fortsetter telleren fremover, mens utgangen fra integratoren fortsetter å synke med konstant hastighet, til den går under referansespenningen til komparatoren. Dette får komparatorutgangen til å endre tilstand og utløser kontrolllogikkfasen for å stoppe tellingen.

Den lagrede digitale størrelsen inne i telleren blir omformerens digitale utgang.

Bruken av et felles klokke- og integratortrinn under både de positive og negative hellingsintervallene tilfører en slags kompensasjon for å kontrollere driften av klokkefrekvensen og nøyaktighetsgrensen til integratoren.

Det kan være mulig å skalere telleutgangen i henhold til brukerens preferanse ved hensiktsmessig å sette opp referanseinngangsverdien og klokkefrekvensen. Vi kan ha disken som binær, BCD eller i annet digitalt format, hvis det er nødvendig.

Bruke Ladder Network

Stigenettverksmetoden ved bruk av teller- og komparatorstadier er en annen ideell måte å implementere analog-til-digital konvertering. I denne metoden begynner en teller å telle fra null, som driver et stigenettverk, og genererer en trinnvis økende spenning, som ligner en trapp (se figur nedenfor).

Prosessen lar spenningen øke med hvert telletrinn.

En komparator overvåker denne økende trappespenningen og sammenligner den med den analoge inngangsspenningen. Så snart komparatoren oppdager trappespenningen som går over den analoge inngangen, ber utgangen om å stoppe tellingen.

Tellerverdien på dette tidspunktet blir den digitale ekvivalenten til det analoge signalet.

Endringsnivået i spenningen som genereres av trinnene til trappesignalet bestemmes av mengden tellebiter som brukes.

For eksempel vil en 12-trinns teller med 10 V referanse betjene et 10-trinns stigenettverk med trinnspenninger på:

Vref/to12= 10 V / 4096 = 2,4 mV

Dette vil skape en konverteringsoppløsning på 2,4 mV. Tiden som kreves for utførelsen av konverteringen bestemmes av tellerens klokkefrekvens.

Hvis klokkefrekvensen på 1 MHz brukes til å betjene en 12-trinns teller, vil den maksimale tiden det tar for konverteringen være:

4096 x 1 μs = 4096 μs ≈ 4,1 ms

Det minste antall konverteringer som kan være mulig per sekund kan bli funnet som:

Nei. av konverteringer = 1 / 4,1 ms ≈ 244 konverteringer / sekund

Faktorer som påvirker konverteringsprosessen

Tatt i betraktning at noen konvertering kan kreve høyere og noen kan kreve lavere tellingstid, kan vanligvis en konverteringstid = 4,1 ms / 2 = 2,05 ms være en god verdi.

Dette vil gi et 2 x 244 = 488 antall konverteringer i gjennomsnitt.

Lavere klokkefrekvens vil bety færre konverteringer per sekund.

En omformer som arbeider med lavere antall teller (lav oppløsning) vil ha en høyere konverteringsfrekvens.

Presisjonen til omformeren bestemmes av nøyaktigheten til kompartoren.

Forrige: Hvordan beregne ferrittkjerne-transformatorer Neste: Ultrasonic Fuel Level Indicator Circuit