MicroBlaze-prosessoren ble utviklet i 2002 for å integrere flere kompliserte funksjoner for å møte nye så vel som økende markedsetterspørsel. Så, MicroBlaze-prosessoren er et viktig element i Low-End Portfolio av Xilinx for å muliggjøre raskere systemutvikling som inneholder Artix®-7 FPGAer , Spartan®-6, Zynq®-7000 AP SoCs. Denne prosessoren er ekstremt konfigurerbar, så den kan brukes som en innebygd prosessor eller mikrokontroller i FPGA-er og også brukes som en co-prosessor i Zynq-7000 AP SoCs basert på ARM Cortex-A9. Denne artikkelen gir kort informasjon om MicroBlaze-prosessor – arkitektur og arbeid med applikasjoner.

Hva er Microblaze-prosessor?

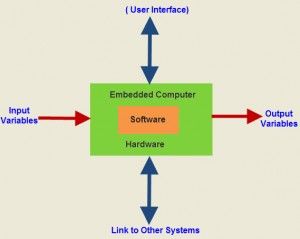

Den myke mikroprosessoren som hovedsakelig er designet for FPGA-er fra Xilinx er kjent som MicroBlaze-prosessoren. Denne prosessoren er ganske enkelt implementert i den generelle minne- og logikkstrukturen til FPGA-er til Xilinx. Denne prosessoren ligner på DLX-arkitekturen basert på RISC og den har et fleksibelt sammenkoblingssystem slik at den støtter forskjellige innebygde applikasjoner. Hoved-I/O-bussen og AXI-forbindelsen til MicroBlaze er en minnetilordnet transaksjonsbuss med en master-slave-fasilitet.

MicroBlaze bruker en dedikert LMB-buss for å få tilgang til lokalt minne og gir rask lagring på brikken. Mange deler av denne prosessoren kan brukerkonfigureres som størrelsen på hurtigbufferen, dybden på pipeline-minneadministrasjonsenheten, innebygde perifere enheter og bussgrensesnitt.

Microblaze-funksjoner

De funksjoner til Microblaz e inkludere følgende. Den har 32 generelle registre.

- Den har 32-bits instruksjonsord inkludert 2 adresseringsmoduser og 3 operander.

- Adressebussen er 32-bit.

- Den har 3-trinns rørledning eller en 5-trinns rørledning.

- En ALU-blokkenhet med skifter.

- Harvard-arkitekturen inkluderer 32-biters data og adressebuss.

- Datagrensesnitt og LMB eller lokal minnebussinstruksjon.

- AX14 og AX14 strømgrensesnitt.

- Flytepunktsenhet og minnestyringsenhet.

- Den støtter låsetrinn.

- Feilsøking og sporingsgrensesnitt.

Microbaze arkitektur

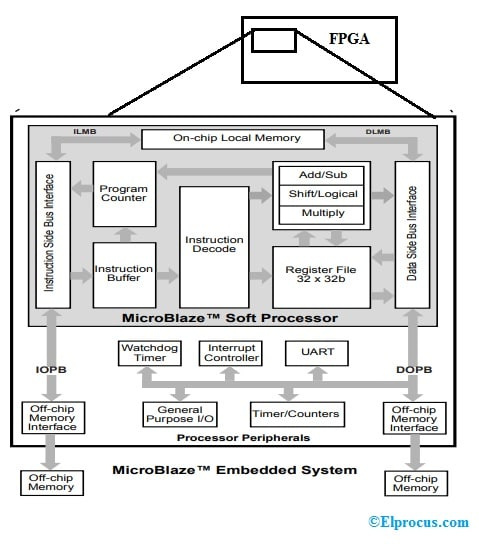

Blokkskjemaet til MicroBlaze-prosessoren er vist nedenfor. Denne MicroBlaze-prosessoren er ekstremt tilpassbar og den støtter over 70 designalternativer. Denne arkitekturen viser permanente maskinvarefunksjoner så vel som konfigurerbare alternativer som instruksjons- eller databuffer, minneadministrasjonsenheten, flytepunktsenheten, etc.

An integrert system satt sammen rundt en MicroBlaze-prosessor inkluderer hovedsakelig MicroBlaze Soft Processor Core, On-chip Local Memory, Standard Bus Interconnects og OPB Peripherals (On-chip Peripheral Bus). Et MicroBlaze-prosessorsystem spenner hovedsakelig fra en kjerne av prosessor med et lokalt minne til et stort system som inkluderer flere MicroBlaze prosessorer , eksternt minne og mange OPB-tilbehør.

Myk prosessorkjerne

Den myke prosessorkjernen til MicroBlaze er sentral i det innebygde MicroBlaze-systemet. Dette er en veldig rask og effektiv 32-bits RISC-prosessor som har følgende funksjoner.

- Instruksjonssettet er ortogonalt.

- Separate data- og instruksjonsbusser.

- 32-bits registre for generell bruk.

- Den har en valgfri komplett 32-bits løpsskifter.

- Innebygde grensesnitt til rask OCM eller on-chip minne og IBMs industristandard OPB (On-chip Peripheral Bus).

Implementeringer innenfor Virtex-II og etterfølgende enheter støtter multiplisering av maskinvare.

On-chip lokalt minne

Det synkrone minnet er et lokalt minne som hovedsakelig brukes for å tillate on-chip Block RAM.

Standard bussforbindelser

Bussgrensesnittene på instruksjons- og datasiden inkluderer et grensesnitt til lokalt minne som kalles LMB (Local Memory Bus) og et grensesnitt til On-chip Peripheral Bus til IBM. Så vi kan designe systemer som strengt tatt holder seg til Harvard-arkitekturen, ellers, for å dele ressurser, kan vi bruke en enkelt OPB i kombinasjon gjennom en buss-arbiter.

Den lokale minnebussen gir garantert en-syklus inngang for on-chip blokk RAM. Dette er en veldig effektiv, enkel og enkelt-master bussprotokoll, og den er perfekt for grensesnitt med raskt lokalt minne. OPB eller On-chip Peripheral Bus er en 32-bit bred multi-master buss som er perfekt for å forene periferiutstyr og eksternt minne til kjernen av MicroBlaze-prosessoren.

On-chip perifer bus periferiutstyr

MicroBlaze-maskinvaresystemet kompletteres av OPB-tilbehør for å gi forskjellige funksjoner som Watchdog Timer eller Timebase, General purpose Timer eller Counters, IC (Interrupt Controller), forskjellige kontrollere som SRAM, Flash Memory, ZBT Memory, BRAM, DDR, SDRAM, UART Lite , SPI, I2C, generell I/O, UART 16450/550 og Ethernet 10/100 MAC. I tillegg kan vi også legge til og definere periferiutstyr hovedsakelig for tilpassede funksjoner, ellers et grensesnitt til et design som finnes i FPGA.

Microblaze instruksjonssett

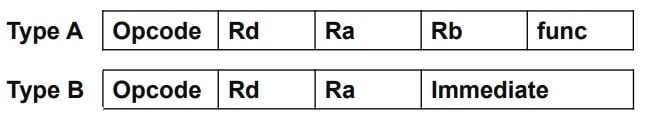

Microblaze instruksjonssett er aritmetikk, logikk, gren, last/lager og andre. Størrelsen på alle instruksjonene er fast. På det meste kan 3-registre gis som operander. Microblaze inkluderer to instruksjonsformater Type A og Type B som er vist nedenfor.

Type A-instruksjonsformat brukes hovedsakelig for registerregisterinstruksjoner. Så det inkluderer opcode, enkelt destinasjon og to kilderegistre. Type B-instruksjonsformat brukes hovedsakelig for registerumiddelbare instruksjoner som inkluderer opcode, enkeltdestinasjon og enkeltkilderegistre.& en 16-bits umiddelbar verdikilde.

I de to ovennevnte instruksjonsformatene er opkoden en operasjonskode, Rd er et destinasjonsregister som er kodet med 5-biter, Ra & Rb er kilderegistre hvor hver kodet med 5-biter og Immediate er en 16-bits verdi.

Aritmetiske instruksjoner

Aritmetiske instruksjoner av type A og type B er gitt nedenfor.

Type A

|

ADD Rd, Ra, Rb legge til |

Rd = Ra+Rb, bæreflagg påvirket |

|

ADD K Rd, Ra, Rb Legg til og behold bære |

Rd = Ra+Rb, bæreflagg påvirkes ikke |

| RSUB Rd, Ra, Rb Omvendt trekke fra |

Rd = R-Rb, bæreflagg påvirkes ikke |

Type B

|

ADD I Rd, Ra, Imm legge til umiddelbart |

Rd = Ra+signExtend32 (Imm) |

|

ADD IK Rd, Ra, Imm legg til umiddelbart og behold bære |

Rd = Ra+ tegnExtend32 (Imm) |

| RSUBIK Rd, Ra, Imm omvendt trekke fra med umiddelbar |

Rd = Ra+ tegnExtend32 (Imm) -Ra |

| SRA Rd, Ra aritmetisk skift til høyre |

Rd = (Ra>>1) |

Logiske instruksjoner

Type A og Type B logiske instruksjoner er gitt nedenfor.

Type A

|

ELLER Rd, Ra, Rb Logisk eller |

Rd = Ra| Rb |

|

OG Rd,Ra,Rb Logisk tillegg |

Rd = Ra & Rb |

| XOR Rd, Ra, Rb Logoisk xor |

Rd = Rb ^ Rb |

| ANDN Rd, Ra, Rb Logisk og ikke |

Rd = Ra & (Rb) |

Type B

|

ORI Rd, Ra, Imm logisk ELLER med umiddelbar |

Rd = Ra | signExtend32 (Imm) |

| ANDI Rd, Ra, Imm logisk OG med umiddelbar |

Rd = Ra & signExtend32 (Imm) |

| XORI Rd, Ra, Imm logoisk XOR med umiddelbar |

Rd = Ra ^ signExtend32 (Imm) |

| ANDNI Rd, Ra, Imm Logisk OG IKKE med umiddelbar |

Rd = Ra & (signExtend32 (Imm)) |

Avdelingsinstruksjoner-Ubetinget

Endre programtellerregisteret

| BRID Imm filial umiddelbart med umiddelbar forsinkelse |

PC = PC+ signExtend32 (Imm) tillate forsinket utførelse av spor |

| BRLID Rd, Imm gren og kobling umiddelbart med umiddelbar forsinkelse (funksjonsanrop) |

Rd = PC PC = PC+& signExtend32 (Imm) tillate forsinket utførelse av spor |

| RTSD Ra, Imm retur fra subrutine |

PC = Ra + signExtend32 (Imm) tillate forsinket utførelse av spor |

| RTID Ra, Imm tilbake fra avbrudd |

PC = Ra + signExtend32 (Imm) tillate forsinket utførelse av spor sett avbruddsaktivering i MSR |

Avdelingsinstruksjoner-Ubetinget1

Endre programtellerregisteret når en betingelse er oppfylt

| BEQI Ra, Imm gren hvis lik |

PC = PC+ signExtend32 (Imm) Hvis Ra = = 0 |

| MASH Ra, Imm gren hvis ikke lik |

Rd = PC PC = PC+& signExtend32 (Imm) Hvis Ra! = 0 |

Avdelingsinstruksjoner-Ubetinget2

Endre programtellerregisteret når en betingelse er oppfylt

| BLTI Ra, Imm gren hvis lavere enn |

PC = PC+ signExtend32 (Imm) Hvis Ra < 0 |

| BLEI Ra, Imm gren hvis lavere lik enn |

Rd = PC PC = PC+& signExtend32 (Imm) Hvis Ra!< = 0 |

| BGTI Ra, Imm gren hvis større enn |

PC = PC+ signExtend32 (Imm) Hvis Ra!> 0 |

| BGEI Ra, Imm gren hvis større lik enn |

PC = PC+signExtend32 (Imm) Hvis Ra!>= 0 |

Laste-/butikkinstruksjoner - Type A

| LW Rd, Ra, Rb Last inn ord |

Adresse = Ra+Rb Rd = *Adresse |

| SW Rd, Ra, Rb Lagre ord |

Adresse – Ra+Rb *Adresse = Rd |

Type B

| LWI Rd, Ra, Imn Last inn ordet umiddelbart |

Adresse = Ra + signExtend32 (Imm) Rd = *Adresse |

| SW Rd, Ra, Imm Lagre ordet umiddelbart |

Adresse = Ra + signExtend32 (Imm) *Adresse = Rd |

Andre instruksjoner

| IMM, Imm umiddelbar |

Utvid Imm for en foregående type B-instruksjon til 32-biter. |

| MFS Rd, Sa Flytte fra spesialregisteret |

Rd = Sa Sa- spesialformålsregister, kildeoperand

|

| MTS Sd, Ra Flytt til spesialregister |

Sd = Ra Sd – spesialregister, destinasjonsoperand |

Registrerer

Arkitekturen til MicroBlaze-prosessoren er helt ortogonal, som inkluderer 32-bits registre for generelle formål og 32-biters spesialregistre som Program Counter & Machine Status Register.

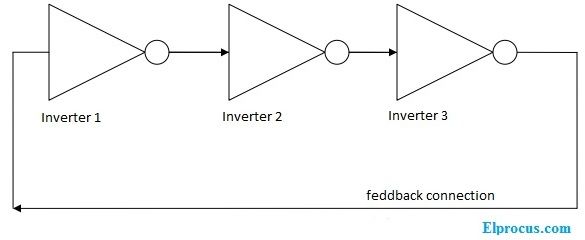

Rørledningsarkitektur

MicroBlaze bruker en 3-trinns rørledningsarkitektur inkludert henting, dekoding og komplette stadier. Datavideresending, grener og rørledningsstopp bestemmes automatisk i maskinvaren.

Last eller butikkarkitektur

MicroBlaze støtter minne i tre datastørrelser 8 bits (Byte), 16 bits (Halvord) og 32 bits (Word). Så minnetilganger er alltid datastørrelsesjustert. Dette er en Big-Endian-prosessor som bruker adressen til Big-Endian-adressen samt merkekonvensjoner når den har tilgang til minnet.

Avbryter

Når et avbrudd finner sted, vil denne prosessoren avslutte den nåværende utførelsen for å administrere avbruddsforespørselen gjennom forgrening for å avbryte vektoradressen og lagre instruksjonsadressen som må utføres. Denne prosessoren vil stoppe fremtidige avbrudd ved å fjerne IE (Interrupt Enable)-flagget i MSR (Machine Status Register).

Hvordan fungerer Microblaze?

MicroBlaze-prosessoren støtter 32-bits bussbredde og denne prosessorkjernen er en RISC-basert motor som inkluderer en registerfil basert på 32-bits LUT RAM gjennom separate instruksjoner for minne og datatilgang.

Denne prosessoren støtter ganske enkelt både on-chip BlockRAM og eksternt minne. Ligner på IBM PowerPC; alle periferiutstyr bruker den lignende CoreConnect OPB-bussen så; periferiutstyret til prosessoren er godt matchet med PowerPC på Virtex-II Pro.

MicroBlaze-prosessoren gir full fleksibilitet til å velge kombinasjonen av minne, periferiutstyr og grensesnittfunksjoner som vil gi deg det nøyaktige systemet du trenger på en enkelt FPGA med lavere kostnader.

Forskjellen S/H Microblaze Vs Risc-V

De forskjellen mellom MicroBlaze og RISC v Inkluder følgende.

|

Microblaze |

Risc-V |

| Det er en myk mikroprosessorkjerne hovedsakelig designet for Xilinx FPGA.

|

RISC-V er en instruksjonssettarkitektur forankret i RISC-prinsipper.

|

| Den bruker Harvard RISC-arkitektur. | Den bruker instruksjonssettarkitektur. |

| Lisensen er proprietær (Xilinx) | Lisensen er åpen kildekode. |

| Dybden på rørledningen er 3 eller 5. | Dybden på rørledningen er 5. |

| Ytelsen er 280 DMIPs. | Ytelsen er 250 DMIPs. |

| Hastigheten er 235 MHz. | Hastigheten er 250 MHz. |

| Den har 1027 LUT-er. | Den har 4125 LUT-er. |

| Implementeringen av teknologien som brukes er Xilinx FPGA. | Implementeringen av teknologien som brukes er FPGA/ASIC. |

Microblaze Fordeler

De fordelene med MicroBlaze Inkluder følgende.

- Det er økonomisk.

- Den er svært konfigurerbar.

- Ytelsen er høy sammenlignet med ARM.

- Den støttes av et innebygd utviklingssett.

- Det er en myk mikroprosessor kjerne.

- For å hjelpe deg raskt å ordne applikasjonen din, inkluderer denne prosessoren tre faste konfigurasjoner som er relatert til velkjente prosessorklasser mikrokontroller, sanntid og applikasjonsprosessor.

Microblaze-applikasjoner

De applikasjoner av MicroBlaze Inkluder følgende.

- Denne prosessoren oppfyller mange forskjellige applikasjonskrav som industri, bil, medisinsk og forbruker, etc.

- Applikasjonene til MicroBlaze spenner fra enkle tilstandsmaskiner basert på programvare til komplekse kontrollere som brukes i innebygde applikasjoner eller Internett-baserte apparater.

- Den er optimalisert for innebygde applikasjoner som industriell kontroll, kontorautomatisering og bilindustri.

- MicroBlaze er i stand til å kommunisere med et stort sett med periferiutstyr for å passe inn i mellomstore applikasjoner.

- Den myke naturen til denne prosessoren gjør den tilpassbar for ulike applikasjoner der designere kan utveksle funksjoner for størrelse for å møte pris- og ytelsesmål for medisinske, bil-, industri- og sikkerhetsapplikasjoner.

Altså handler dette om en oversikt over Microblaze prosessor. Dette er en fullt utstyrt 32-bits programmerbar RISC myk prosessorkjerne. Denne prosessoren oppfyller ulike krav innenfor ulike felt som forbruker-, medisinsk-, industri-, bil- og kommunikasjonsinfrastrukturmarkeder. Den er ekstremt konfigurerbar, så brukt som den innebygde prosessoren eller mikrokontrolleren i FPGA-er ellers som en co-prosessor for ARM. Her er et spørsmål til deg, hva er FPGA?