Generelt er full subtraktor en av de mest brukte og essensielle kombinasjonslogikkretser . Det er en grunnleggende elektronisk enhet, som brukes til å trekke fra to binære tall. I den tidligere artikkelen har vi allerede gitt den grunnleggende teorien om halv hugger & en full hugger som bruker binære sifre for beregningen. Likeledes bruker full-subtraktoren binære sifre som 0,1 for subtraksjonen. Kretsen til dette kan bygges med logiske porter som OR, Ex-OR, NAND gate. Inngangene til denne subtraktoren er A, B, Bin og utgangene er D, Bout.

Denne artikkelen gir en full-subtraktor teoriidee som omfatter premissene som hva som er en subtraktor, design med logiske porter, sannhetstabell, etc. Denne artikkelen er nyttig for ingeniørstudenter som kan gå gjennom disse emnene i HDL Practical lab.

Hva er en subtraktor?

Binærsifret subtraksjon kan gjøres ved hjelp av subtraktorkretsen. Dette er en slags kombinasjonslogisk krets, brukt til å utføre subtraksjon av to binære sifre som 0s og 1s. Subtraksjon av binære sifre fra 0 til 0 eller 0 til 1 endrer ikke resultatet, subtraksjon fra 1 til 1 vil resultere som 0, men subtraksjonen fra 1 til 0 trenger lån.

For eksempel inkluderer to-bits subtraktorkrets to innganger som A & B, mens utgangene er forskjellig og lånt. Denne kretsen kan bygges med tilleggere sammen med omformere som er lokalisert blant alle datainngangene samt låne (Bin) -inngang fra den tidligere fasen av FA.

Subtraktorer er klassifisert i to typer som halv subtraktor og full subtraktor. Her diskuterer vi hele subtraktoren.

Hva er en full subtraktor?

Det er en elektronisk enhet eller logikkrets som utfører subtraksjon av to binære sifre. Det er en kombinasjonslogikkrets som brukes i digital elektronikk. Mange kombinasjonskretser er tilgjengelige i integrert krets teknologi nemlig addere, kodere, dekodere og multiplexere. I denne artikkelen skal vi diskutere konstruksjonen ved hjelp av halv subtraktor og også begrepene som sannhetstabell.

Full subtraktor

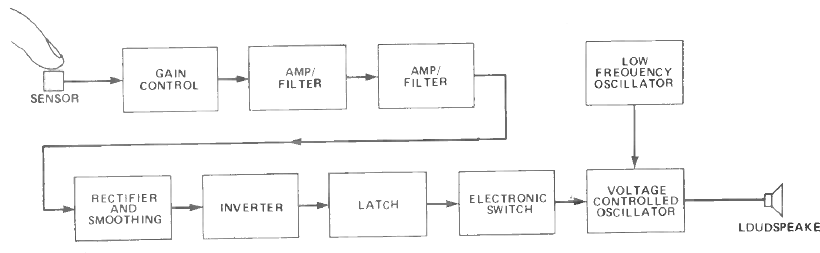

Utformingen av dette kan gjøres av to halve subtraktorer, som involverer tre innganger som minuend, subtrahend og lån, lånebit blant inngangene er oppnådd fra subtraksjonen av to binære sifre og trekkes fra neste par med høyere ordre biter, utganger som differanse og lån.

De fullt subtraktorblokkdiagram er vist nedenfor. Den største ulempen med halvtrakteren er at vi ikke kan gjøre en lånebit i denne subtraktoren. Mens vi i utformingen faktisk kan lage en lånebit i kretsen og kan trekke fra de resterende to i / ps. Her er A minuend, B er subtrahend & Bin lånes inn. Utgangene er Difference (Diff) & Bout (Borrow out). Den komplette subtraktorkretsen kan oppnås ved å bruke to halvtrekkere med en ekstra ELLER-port.

Komplett subtraktorkretsdiagram med logiske porter

De kretsskjema over hele subtraktoren ved hjelp av grunnleggende gate s er vist i det følgende blokkdiagrammet. Denne kretsen kan gjøres med to halvtraktorkretser.

I den første halvtrekkerkretsen er de binære inngangene A og B. Som vi har diskutert i forrige halvtrekksartikkel, vil den generere to utganger, nemlig differanse (Diff) & Låne.

Full subtraktor ved hjelp av Logic Gates

Differansen o / p for den venstre subtraktoren er gitt til den venstre halvtrekkskretsen. Diff-utgang leveres videre til inngangen til den høyre halvdelstraktorkretsen. Vi tilbød Lån i litt over den andre i / p av den neste halv subtraktorkrets . Nok en gang vil det gi Diff ut i tillegg til å låne ut litt. Den endelige produksjonen til denne subtraktoren er Diff-output.

På den annen side er lånet fra begge de halve subtraktorkretsene koblet til ELLER logikkporten. Senere enn å gi ut ELLER logikk for to utgangsbiter av subtraktoren, får vi den endelige lånet ut av subtraktoren. Den siste lånet ut for å betegne MSB (en mest betydelig bit).

Hvis vi observerer den interne kretsen til dette, kan vi se to halvtrekkere med NAND-port og XOR-port med en ekstra ELLER-port.

Full Subtractor Truth Table

Dette subtraktorkrets utfører en subtraksjon mellom to bits, som har 3 innganger (A, B og Bin) og to utganger (D og Bout). Her angir inngangene minuend, subtrahend og tidligere lån, mens de to utgangene er betegnet som lån o / p og differanse. Følgende bilde viser sannhetstabellen til fulltrakteren.

Innganger | Utganger | |||

Minuend (A) | Subtrahend (B) | Lån (søppel) | Forskjell (D) | Lån (Bout) |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

K-Map

Forenkling av full subtraktor K-kart for ovennevnte forskjell og lån er vist nedenfor.

Ligningene for forskjellen så vel som Bin er nevnt nedenfor.

Uttrykket for forskjell er,

D = A’B’Bin + AB’Bin ’+ A’BBin’ + ABBin

Uttrykket for Lån er,

Bout = A’Bin + A’B + BBin

Cascading of Full Subtractor Circuit

Tidligere har vi diskutert en oversikt over dette som konstruksjon, kretsskjema med logiske porter. Men hvis vi ønsker å trekke fra to ellers flere 1-bits tall, er denne subtraktorkretsen veldig nyttig for å kaskade enkeltbitnumre og trekker også mer enn to binære tall. I slike tilfeller brukes en full adder-kaskadekrets med hjelp av IKKE logisk gate. Konvertering av kretsen fra fulladder til full subtraktor kan gjøres ved hjelp av 2’s komplementteknikk.

Generelt sett inverterer du subtrahend-inngangene for fulladderen ved å bruke IKKE gate, ellers en inverter. Ved å legge til denne Minuend (ikke-invertert inngang) & Subtrahend (Invertert inngang), er LSB (bæreinngang) til FA-kretsen 1, noe som betyr Logisk høy ellers trekker vi to binære sifre ved hjelp av 2’s komplementteknikk. FAs produksjon er Diff-biten, og hvis vi inverterer gjennomføringen, kan vi få MSB ellers Låne-biten. Egentlig kan vi designe kretsen slik at utdata kan observeres.

Verilog-kode

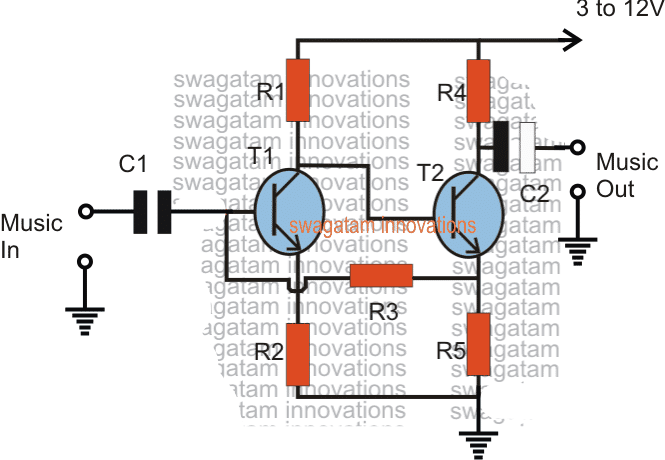

For kodingsdelen må vi først sjekke den strukturelle måten å modellere det logiske kretsskjemaet på. Logikkdiagrammet for dette kan bygges ved hjelp av en AND-gate, halve subtraktorkretser og kombinasjonen av logiske porter som AND, OR, NOT, XOR-porter. Som i strukturell modellering forklarer vi forskjellige moduler for alle grunnleggende elementære ordninger. I den følgende koden kan forskjellige moduler defineres for hver gate.

Denne modulen er for ELLER-porten.

INNGANG: a0, b0

UTGANG: c0

Til slutt vil vi forene disse portnøyaktige modulene til en eneste modul. For det bruker vi her instantiering av modulen. Nå kan denne instantieringen brukes når vi ønsker å replikere en nøyaktig modul eller funksjon for forskjellige inngangssett. Først designer vi en halv subtraktor, så brukes denne modulen til å implementere en full subtraktor. For å implementere dette bruker vi ELLER-porten til å kombinere o / ps for variabelen til Bout. De verilog-kode for hele subtraktoren er vist nedenfor

modul or_gate (a0, b0, c0)

inngang a0, b0

utgang c0

tilordne c0 = a0 | b0

endemodul

modul xor_gate (a1, b1, c1)

inngang a1, b1

utgang c1

tilordne c1 = a1 ^ b1

endemodul

modul og_gate (a2, b2, c2)

inngang a2, b2

utgang c2

tilordne c2 = a2 & b2

endemodul

modul not_gate (a3, b3)

inngang a3

utgang b3

tilordne b3 = ~ a3

endemodul

modul halv_subtraktor (a4, b4, c4, d4)

inngang a4, b4

utgang c4, d4

ledning x

xor_gate u1 (a4, b4, c4)

og_gate u2 (x, b4, d4)

not_gate u3 (a4, x)

endemodul

modul full_subtractor (A, B, Bin, D, Bout)

inngang A, B, søppel

utgang D, Bout

ledning p, q, r

halv_subtraktor u4 (A, B, p, q)

halv_subtraktor u5 (p, Bin, D, r)

eller_gate u6 (q, r, Bout)

endemodul

Full subtraktor ved bruk av 4X1 Multiplexer

Utførelsen av subtraksjon kan gjøres gjennom de to komplementmetoden. Dermed krever vi bruk av en 1-XOR-port som brukes til å invertere 1-bit og inkludere en i bærebit. Utgangen fra DIFFERENCE er lik output SUM i full adderkrets, men BARROW o / p er ikke lik fulladders bæreoutput, men den er invertert så vel som komplimentert, som A - B = A + (-B) = A + tos komplement av B.

Utformingen av dette ved hjelp av 4X1 multiplexer er vist i det følgende logiske diagrammet. Denne utformingen kan gjøres ved hjelp av følgende trinn.

4X1 multiplekser

- I trinn 1 er det to utganger som Sub og Lån. Så vi må velge to multipleksere.

- I trinn 2 kan sannhetstabellen implementeres sammen med K-maps

- I trinn 3 kan de to variablene velges som din valgte linje. For eksempel er B & C i dette tilfellet.

Sannhetstabell

De sannhetstabell med full subtraktor krets som bruker 4X1 multiplexer inkluderer følgende

TIL | B | C | Under | Låne |

0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

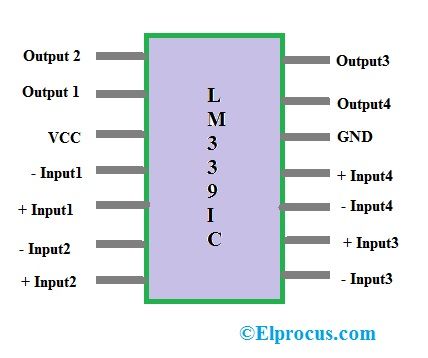

Full subtraktor ved hjelp av dekoder

Utformingen av en full subtraktor med 3-8 dekodere kan gjøres ved hjelp av aktive lave utganger. La oss anta at dekoderen fungerer ved å bruke følgende logikkdiagram. Dekoderen inkluderer tre innganger i 3-8 dekodere. Basert på sannhetstabellen kan vi skrive mintermer for resultatene av forskjell og lån.

Fra sannhetstabellen ovenfor,

For de forskjellige funksjonene i sannhetstabellen kan mintermer skrives som 1,2,4,7, og på samme måte for lån kan mintermer skrives som 1,2,3,7. 3-8 dekoderne inkluderer tre innganger samt 8 utganger lik0 til 7 tall.

3-til-8 dekoder

Hvis inngangen til subtraktoren er 000, vil utgangen '0' være aktiv, og hvis inngangen er 001, vil utgangen '1' være aktiv.

Nå kan utgangene til subtraktoren tas fra 1, 2, 4 og 7 for å koble den til en NAND-port, så vil utgangen være forskjellen. Disse utgangene kan kobles til andre NAND-logiske porter der utgangen endres til lånet.

For eksempel, hvis inngangen er 001, vil utgangen være 1 som betyr at den er aktiv. Så utgangen er aktiv lav, og utgangen kan fås fra NAND-porten kalt differansefunksjon som høy og lånefunksjon endres også til å være høy. Derfor får vi den foretrukne produksjonen. Så til slutt fungerer dekoderen som en full subtraktor.

Fordeler og ulemper

De fordelene med subtraktoren Inkluder følgende.

- Prosjekteringen av subtraktoren er veldig enkel og implementere

- Effektfradrag innen DSP (digital signalbehandling)

- Beregningsoppgaver kan utføres i høy hastighet.

De ulemper med subtraktoren Inkluder følgende.

- I halvtrakteren er det ingen vilkår for å akseptere lånelignende innspill fra den tidligere fasen.

- Subtraktorhastigheten kan være delvis gjennom forsinkelsen i kretsen.

applikasjoner

Noen av applikasjoner av full-subtractor Inkluder følgende

- Disse brukes vanligvis for ALU (Arithmetic logic unit) i datamaskiner for å trekke fra som CPU og GPU for applikasjoner av grafikk for å redusere kretsproblemet.

- Subtraktorer brukes mest til å utføre aritmetiske funksjoner som subtraksjon, i elektroniske kalkulatorer så vel som digitale enheter.

- Disse gjelder også for forskjellige mikrokontrollere for aritmetisk subtraksjon, tidtakere og programtelleren (PC)

- Subtraktorer brukes i prosessorer for å beregne tabeller, adresser, etc.

- Det er også nyttig for DSP og nettverksbaserte systemer.

- Disse brukes hovedsakelig for ALU innen datamaskiner for å trekke fra som CPU og GPU for grafiske applikasjoner for å redusere kompleksiteten i kretsen.

- Disse brukes hovedsakelig til å utføre aritmetiske funksjoner som subtraksjon innen digitale enheter, kalkulatorer, etc.

- Disse subtraktorene er også passende for forskjellige mikrokontrollere for timere, PC (programteller) og aritmetisk subtraksjon

- Disse brukes for prosessorer for å beregne adresser, tabeller osv.

- Implementeringen av dette med logiske porter som NAND & NOR kan gjøres med en hvilken som helst full subtraktorlogikkrets fordi begge NOR & NAND-portene kalles universalporter.

Fra den ovennevnte informasjonen, ved å evaluere addereren, full subtraktor ved hjelp av to halve subtraktorkretser og dens tabellformer, kan man legge merke til at Dout i full-subtraktoren er nøyaktig lik Sout av fulladderen. Den eneste variasjonen er at A (inputvariabel) suppleres i full-subtraktoren. Dermed er det oppnåelig å endre fulladderkretsen til en full-subtraktor ved å bare komplementere i / p A før den blir gitt til logikkportene for å generere den siste utlånsbiten (Bout).

Ved å bruke en hvilken som helst logikkrets for full subtraktor, kan full subtraktor ved bruk av NAND-porter og full subtraktor med nor-porter implementeres, siden både NAND- og NOR-portene blir behandlet som universale porter. Her er et spørsmål til deg, hva er forskjellen mellom halv subtraktor og full subtraktor?

![24 V til 12 V DC-omformerkrets [ved bruk av bryterregulator]](https://electronics.jf-parede.pt/img/3-phase-power/F1/24-v-to-12-v-dc-converter-circuit-using-switching-regulator-1.jpg)