Teller er en digital enhet, og utgangen fra telleren inkluderer en forhåndsdefinert tilstand basert på klokkepulsapplikasjonene. Resultatet av teller kan brukes til telle antall pulser. Generelt består tellere av et flip-flop-arrangement som kan være synkronteller asynkronteller. I synkron teller blir bare en klokke i / p gitt til alle flip-flops, mens i asynkron teller er o / p av flip flop er klokkesignalet fra det nærliggende. Søknadene til mikrokontrolleren trenger telling av utvendige hendelser som nøyaktig intern tidsforsinkelse og frekvensen til pulstogene. Disse hendelsene brukes ofte i digitale systemer og datamaskiner. Begge disse hendelsene kan utføres med programvareteknikker, men programvaresløyfer for telling vil ikke gi det eksakte resultatet litt viktigere funksjoner blir ikke gjort. Disse problemene kan løses ved hjelp av tidtakere og tellere i mikrokontrollerne som brukes som avbrudd.

Teller

Typer tellere

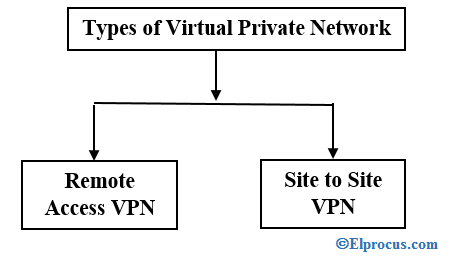

Teller kan kategoriseres i forskjellige typer i henhold til måten de blir klokket på. De er

- Asynkrone tellere

- Synkrone tellere

- Asynkrone tiårsmøter

- Synkrone tiårsteller

- Asynkrone opp-ned-tellere

- Synkron opp-ned tellere

For bedre forståelse av denne typen tellere, her diskuterer vi noen av tellerne.

Asynkrone tellere

Diagrammet til en 2-biters asynkron teller er vist nedenfor. Den utvendige klokken er bare koblet til klokken i / p på FF0 (første flip-flop). Så denne FF endrer tilstanden ved den avtagende kanten av hver klokkepuls, men FF1 endres bare når den aktiveres av den avtagende kanten av Q o / p av FF0. På grunn av den integrerte forplantningsforsinkelsen gjennom en FF, kan endringen av i / p-klokkepulsen og en endring av Qo / p av FF0 aldri skje på nøyaktig samme tid. Så, FF-ene kan ikke aktiveres samtidig, og generere en asynkron operasjon.

Asynkrone tellere

Merk at for enkelhets skyld vises endringene av Q0, Q1 og CLK i diagrammet ovenfor som samtidige, selv om dette er en asynkron teller. Egentlig er det en liten forsinkelse b / n Q0, Q1 og CLK endres.

Vanligvis er alle CLEAR i / ps koblet sammen, så før en telling starter, kan en enkelt puls slette alle FF-ene. Klokkepulsen som mates inn i FF0, rippes gjennom de nye tellerne etter forplantningsforsinkelser, for eksempel en krusning på vannet, derav begrepet Ripple Counter.

Kretsskjemaet for to-bits ringteller inkluderer fire forskjellige tilstander, hver med en telleverdi. På samme måte kan en teller med n FFs ha 2N-tilstander. Antall tilstander i en teller kalles som mod-nummer. Derfor er en to-bits teller en mod-4-teller.

Asynkrone tiårsmøter

I forrige teller har 2n stater. Men teller med tilstander mindre enn 2n er også mulig. Disse er designet for å ha nei. av stater i serien. Disse kalles forkortede sekvenser som oppnås ved å føre telleren til resirkulering før de går gjennom alle dens stater. En vanlig modul for tellere med forkortet sekvens er 10. En teller med 10-tilstander i serien kalles tiårsteller. Den implementerte tiårtellerkretsen er gitt nedenfor.

Asynkron kretsdiagram for tiårsteller

Når telleren teller til ti, blir alle FF-ene ryddet. Legg merke til at bare Q1 og Q3 begge brukes til å dekode antallet 10, som kalles delvis dekoding. Samtidig har en av de andre statene fra 0-9 både Q1 og Q3 vil være høye. Serien til tiårstellerbordet er gitt nedenfor.

Sekvens av tiårstelleren

Asynkrone opp-ned-tellere

I spesielle applikasjoner må en teller kunne telle både opp og ned. Nedenfor kretsen er en tre-biters opp- og nedteller, som teller OPP eller NED basert på styresignalstatusen. Når UP i / p er på 1 og NED i / p er på 0, vil NAND-porten mellom FF0 og FF1 gate den ikke-inverterte o / p (Q) av flip flop (FF0) inn i klokken i / p av flip flop (FF1). På samme måte vil den ikke-inverterte o / p av Flip Flop1 gates gjennom den andre NAND-porten inn i klokken i / p av flip-flop2. Derfor teller telleren opp.

Asynkront kretsdiagram opp og ned

Når kontroll i / p (UP) er på 0 og NED er på 1, blir den inverterte o / ps av flip-flop0 (FF0) og flip-flop1 (FF) gated i klokken i / ps av FF1 & FF2 separat . Hvis FF-er opprinnelig endres til 0’er, vil telleren gå gjennom serien nedenfor når i / p-pulser påføres. Legg merke til at en asynkron opp-ned-teller er tregere enn en UP-teller / ned-teller på grunn av en ekstra forplantningsforsinkelse introdusert av NAND-portene.

Sekvens av den asynkrone opp-ned-telleren

Synkrone tellere

I dette type tellere , er CLK i / ps til alle FF-ene koblet sammen og aktiveres av i / p-pulser. Så alle FF-er endrer øyeblikkelig tilstand. Kretsskjemaet nedenfor er en tre-bits synkron teller. Inngangene J og K på flip-flop0 er koblet til HIGH. Flip-flop 1 har sin J & K i / ps koblet til o / p av flip-flop0 (FF0), og inngangene J & K til flip-flop2 (FF2) er koblet til o / p av en AND-port som mates av o / ps av flip-flop0 og flip-flop1. Når begge utgangene til FF0 og FF1 er HØYE. Den positive kanten av den fjerde CLK-pulsen vil føre til at FF2 endrer tilstanden på grunn av AND-porten.

Synkront motkretsdiagram

Serien til det tre-bits tellerbordet er gitt nedenfor. Den største fordelen med disse tellerne er at det ikke er noen økende tidsforsinkelse på grunn av at alle FF-er er aktivert parallelt. Dermed vil den maksimale driftsfrekvensen til denne synkrontelleren være betydelig høyere enn for den ekvivalente ringtelleren.

CLK Pulses of the Synchronous Counters

Synkrone tiårsteller

Synkron teller teller fra 0-9 som asynkron teller og resirkulerer deretter null. Denne prosessen gjøres ved å kjøre 1010-statene tilbake til 0000-tilstanden. Dette betegnes som avkortet sekvens, som kan utformes av kretsen nedenfor.

Synkront tiår teller kretsdiagram

Fra serien på venstre bord kan vi observere det

- Q0 binder på hver eneste CLK-puls

- Q1 endres på neste klokkepuls hver gang Q0 = 1 og Q3 = 0.

- Q2 endres på neste klokkepuls hver gang Q0 = Q1 = 1.

- Q3 endres på neste CLK-puls hver gang Q0 = 1, Q1 = 1 & Q2 = 1 (telling 7), eller når Q0 = 1 & Q3 = 1 (telling 9).

Sekvens av synkron tiårteller

Ovennevnte egenskaper benyttes med OG port eller ELLER port . Logikkdiagrammet for dette er vist i diagrammet ovenfor.

Synkron opp-ned tellere

En tre-bits synkron opp-ned-teller, tabellform og serie er gitt nedenfor. Denne typen teller har en opp-ned-kontroll i / p som ligner på asynkron opp-ned-teller, som brukes til å kontrollere tellerens retning gjennom en bestemt serie.

Synkront kretsdiagram opp og ned

Serien i tabellen viser

- Q0 binder på hver CLK-puls for både opp- og ned-serien

- Når Q0 = 1 for opp-serien, endres tilstanden til Q1 på neste CLK-puls.

- Når Q0 = 0 for nedserien, endres tilstanden til Q1 på neste CLK-puls.

- Når Q0 = Q1 = 1 for opp-serien, endres tilstanden til Q2 på neste CLK-puls.

- Når Q0 = Q1 = 0 for nedserien, endres tilstanden til Q2 på neste CLK-puls.

Sekvens av synkrone tiårsmøter

Ovennevnte egenskaper brukes med AND-porten, ELLER porten og IKKE porten. Logikkdiagrammet for dette er vist i diagrammet ovenfor.

Anvendelser av tellere

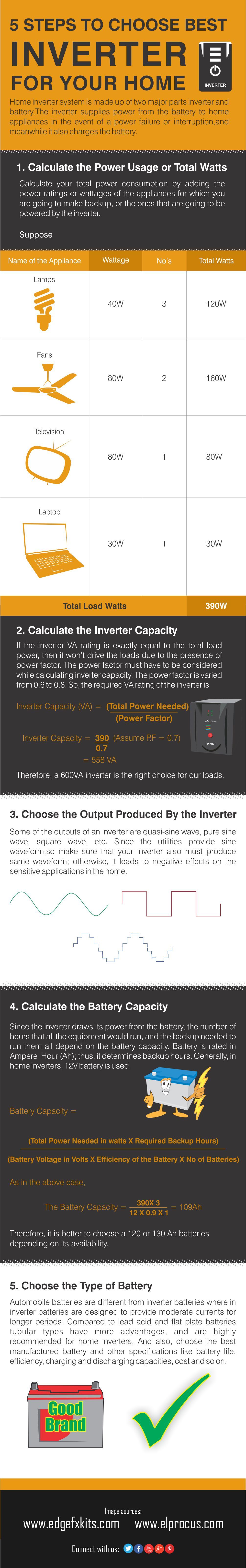

Bruken av tellere involverer hovedsakelig i digitale klokker og i multipleksing. Det beste eksemplet på telleren er parallell med seriell datakonverteringslogikk diskutert nedenfor.

Et sett med biter, som utfører samtidig på parallelle linjer, kalles parallelle data. Et sett med biter, som utføres på en enkelt linje i en tidsserie, kalles seriell data. Parallell-til-seriell datakonvertering gjøres normalt ved å bruke en teller for å gi en binær serie av dataene, velg i / ps til en MUX, som forklart i kretsen nedenfor.

Parallell-til-seriell datakonvertering

I ovenstående krets består modulo-8-telleren av Q o / ps, som er koblet til dataene, velg i / ps av en 8-bit MUX . Den første 8-biters gruppen av parallelle data blir brukt på inngangene til MUX. Når telleren går gjennom en binær serie fra 0-7, starter hver bit med D0, blir valgt i serie og ført gjennom MUX til o / p-linjen. Etter 8-CLK-pulser er databyte endret til et seriell format og sendt ut via overføringslinjen. Deretter bearbeides telleren tilbake til 0 og endrer en annen parallellbyte serielt igjen i den lignende prosessen.

Dermed handler alt om tellere og typer teller, som inkluderer asynkrone tellere, synkronteller, asynkrone tiårtellere, synkron tiårteller, asynkrone opp-ned-tellere og synkron opp-ned-tellere. Videre, enhver tvil angående dette emnet eller tidtakere og tellere i 8051 mikrokontroller vennligst kommenter i kommentarfeltet nedenfor.