RISC V er en instruksjonssettarkitektur utviklet av University of California, Berkeley. Konseptet med RISC var motivert av sannheten om at de fleste prosessorinstruksjonene ikke ble brukt av de fleste dataprogrammer. Så unødvendig dekodingslogikk ble brukt i designene til prosessorer , bruker mer strøm så vel som areal. For å forkorte instruksjonssettet og for å investere mer innenfor registerressurser, kan RISC V-prosessor ble implementert.

Denne teknologien ble lagt merke til av mange teknologigiganter og oppstartsbedrifter fordi den er helt åpen kildekode og gratis. De fleste typer prosessorer er tilgjengelige med en lisensavtale, men med denne typen prosessorer; hvem som helst kan lage sine nye prosessordesign. Så denne artikkelen diskuterer en oversikt over en RISC V-prosessor – som fungerer og dens applikasjoner.

Hva er RISC V-prosessor?

I RISC V-prosessoren står begrepet RISC for 'redusert instruksjonssett datamaskin' som utfører få datamaskininstruksjoner mens 'V' står for 5. generasjon. Det er en åpen kildekode maskinvare ISA (instruction set architecture) basert på det etablerte prinsippet om FARE .

Sammenlignet med andre ISA-design, er denne ISA tilgjengelig med en åpen kildekode-lisens. Så en rekke produksjonsbedrifter har annonsert og også levert RISC-V-maskinvare, med åpen kildekode-operativsystemer.

Dette er en ny arkitektur og er tilgjengelig i åpne, ikke-begrensende og gratis lisenser. Denne prosessoren har omfattende støtte fra brikke- og enhetsprodusenter. Så den er hovedsakelig designet for å være fritt utvidbar og tilpassbar for bruk i mange applikasjoner.

RISC V historie

RISC ble oppfunnet av prof. David Patterson rundt 1980 ved University of California, Berkeley. Prof. David med prof. John Hennessy leverte sin innsats i to bøker, nemlig 'Computer Organization and Design' og 'Computer Architecture at Stanford University. Så de mottok ACM A.M. Turing-prisen i 2017.

Fra år 1980 til 2010-året ble RISCs femte generasjons utviklingsforskning startet og ble til slutt identifisert som RISC-V, som uttales som risiko fem.

RISC V Architecture & Working

RV12 RISC V-arkitekturen er vist nedenfor. RV12 er svært konfigurerbar med en enkeltkjerne RV32I og RV64I-kompatibel RISC CPU som brukes i innebygde felt. RV12 er også fra en 32- eller 64-bits CPU-familie avhengig av industristandard RISC-V-instruksjonssettet.

RV12 utfører ganske enkelt en Harvard-arkitektur for samtidig tilgang til instruksjoner så vel som dataminne. Den inkluderer også en 6-trinns pipeline som hjelper til med å optimalisere overlappinger mellom utførelsen samt minnetilganger for å forbedre effektiviteten. Denne arkitekturen inkluderer hovedsakelig Branch Prediction, Data Cache, Debug Unit, Instruction Cache og valgfrie multiplikator- eller divider-enheter.

Hovedtrekkene til RV12 RISC V inkluderer følgende.

- Det er et industristandard instruksjonssett.

- Parametrisert med 32 eller 64 bit data.

- Den har presise og raske avbrudd.

- Egendefinerte instruksjoner tillater tillegg av proprietære maskinvareakseleratorer.

- Utførelse av enkelt syklus.

- Seks-trinns rørledning med optimaliserende foldet.

- Støtte med minnebeskyttelse.

- Valgfrie eller parametriserte cacher.

- Ekstremt parametrisert.

- Brukere kan velge 32/64-bits data og grenprediksjonsenhet.

- Brukere kan velge instruksjons-/datacacher.

- Brukervalgbar struktur, størrelse og arkitektur for cache.

- Maskinvaredeler eller multiplikatorstøtte etter brukerdefinert ventetid.

- Bussarkitekturen er fleksibel som støtter Wishbone & AHB.

- Denne designen optimerer kraften og størrelsen.

- Designet er fullstendig parametrisert som gir ytelse eller kraftavveininger.

- Gated CLK-design for å redusere kraften.

- Programvarestøtte etter industristandard.

- Arkitektonisk simulator.

- Eclipse IDE brukes for Linux/Windows.

RISC V Execution Pipeline

Det inkluderer fem stadier som IF (instruksjonshenting), ID (instruksjonsdekoding), EX (execute), MEM (minnetilgang) og WB (register-tilbakeskrivning).

Henting av instruksjoner

I Instruction Fetch eller IF-stadiet leses en enkelt instruksjon fra programtelleren (PC) og instruksjonsminnet som oppdateres til neste instruksjon.

Instruksjon Pre-Decode

Når RVC-støtte er tillatt, vil Instruction Pre-Decode-stadiet dekode en 16-bits komprimert instruksjon til en naturlig 32-bits instruksjon.

Instruksjonsdekoding

I instruksjonsdekodingsstadiet (ID) er registerfilen tillatt og omkjøringskontrollene bestemmes.

Henrette

I Utfør-stadiet beregnes resultatet for en ALU-, DIV-, MUL-instruksjon, minnet som er tillatt for en Store- eller Load-instruksjon, og grener og hopp måles mot deres forventede utfall.

Hukommelse

I dette minnestadiet får du tilgang til minnet gjennom rørledningen. Inkluderingen av denne fasen sikrer rørledningens høye ytelse.

Skriv tilbake

I dette stadiet skrives resultatet av utførelsesfasen inn i registerfilen.

Branch Predictor

Denne prosessoren inkluderer en grenprediktorenhet eller BPU som brukes til å lagre tidligere data for å veilede RISC V-prosessoren i å avgjøre om en spesifikk gren er tatt eller ikke. Disse prediktordataene oppdateres ganske enkelt når grenen kjøres.

Denne enheten inkluderer forskjellige parametere som bestemmer dens oppførsel. For eksempel brukes HAS_BPU til å bestemme om en gren forutsier at en enhet er tilstede, BPU_GLOBAL_BITS vil bestemme hvor mange tidligere biter som skal brukes og BPU_LOCAL_BITS vil bestemme hvor mange av LSB-ene til programtelleren som skal brukes. Kombinasjonen av BPU_LOCAL_BITS og BPU_GLOBAL_BITS vil skape en vektor som hovedsakelig brukes til å adressere grenprediksjonstabellen.

Databuffer

Dette brukes hovedsakelig for å øke hastigheten på tilgangen til dataminne ved å bufre nylig åpnede minneplasseringer. Dette er i stand til å håndtere halvords-, byte- og ordtilganger når XLEN = 32 hvis de er på sine egne grenser. Den er også i stand til å håndtere halv-ord, byte, ord og dobbeltord-tilganger når XLEN=64 hvis de er på sine egne grenser.

Gjennom en cache-miss kan en hel blokk skrives tilbake til minnet, så om nødvendig kan en ny blokk lastes inn i cachen. Databufferen deaktiveres ved å sette DCACHE_SIZE til null. Etter det får du tilgang til minneplasseringer direkte gjennom Datagrensesnitt .

Instruksjonsbuffer

Dette brukes hovedsakelig for å fremskynde henting av instruksjoner ved å bufre nylig hentede instruksjoner. Denne hurtigbufferen brukes til å hente én pakke for hver syklus på en hvilken som helst 16-bits grense, men ikke over en blokkgrense. Gjennom en cache-miss kan en hel blokk lastes fra instruksjonsminnet. Konfigurasjonen av denne cachen kan gjøres basert på brukerens behov. Størrelsen på hurtigbufferen, erstatningsalgoritmen og blokklengden kan konfigureres.

Instruksjonssyklusen vil bli deaktivert ved å sette ICACHE_SIZE til null. Etter det hentes pakker direkte fra minnet gjennom Instruksjonsgrensesnitt.

Feilsøkingsenhet

Feilsøkingsenheten lar feilsøkingsomgivelsene stoppe og undersøke CPU'en. Hovedtrekkene til dette er Branch Tracing, Single Step Tracing opp til 8- Hardware Breakpoints.

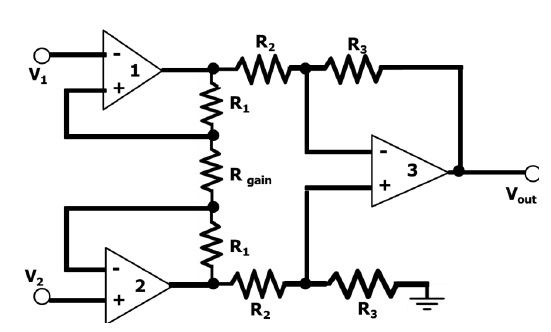

Registrer fil

Dette er designet med 32 registerplasseringer fra X0 til X31 hvor X9 Register alltid er null. Registerfilen inkluderer 1- skriveport og 2- leseporter.

Konfigurerbart grensesnitt

Dette er et eksternt grensesnitt hvor denne prosessoren støtter forskjellige eksterne bussgrensesnitt.

Hvordan fungerer RISC V?

RISC-V er en instruksjonssettarkitektur forankret i RISC-prinsippene (redusert instruksjonssett-computer). Denne prosessoren er veldig unik og også revolusjonerende ettersom den er en gratis, vanlig og åpen kildekode ISA hvor maskinvare kan utvikles, programvaren kan porteres og prosessorer kan designes for å støtte den.

Forskjellen S/H RISC V Vs MIPS

Forskjellen mellom RISC V og MIPS inkluderer følgende.

|

RISC V |

MIPS |

| Begrepet RISC V står for Reduced Instruction Set Computer hvor 'V' er femte generasjon. | Begrepet 'MIPS' står for 'Million instruksjoner per sekund'. |

| RISC-V tillater ganske enkelt produsentene av mindre enheter å designe maskinvare uten å betale. | MIPS lar produsenten måle prosessorens hastighet ved å betale fordi det ikke er gratis. |

| MIPS er effektivt dødt. | RISC-V er ikke effektivt død. |

| Denne prosessoren gir greninstruksjoner for å sammenligne to registre. | MIPS avhenger av en sammenligningsinstruksjon som lokaliserer et register til 1 eller 0 basert på om kontrasten er sann. |

| ISA-kodingsskjemaet er fast og variabelt i RISC V. | ISA-kodingsskjemaet er fikset i MIPS |

| Instruksjonssettstørrelsen er 16-bit eller 32-bit eller 64-bit eller 128-bit. | Størrelsen på instruksjonssettet er 32-bit eller 64-bit. |

| Den har 32 registre for generelle formål og flyttall | Den har 31 registre for generelle formål og flyttall. |

| Den har 26-single og doble presisjon flytepunkt operasjoner. | Den har 15-single og doble presisjon flytepunkt operasjoner. |

Forskjell S/H RISC V Vs ARM

Forskjellen mellom RISC V og ARM inkluderer følgende.

|

RISC V |

VÆPNE |

| RISC-V er åpen kildekode, så den krever ingen lisens. | ARM er en lukket kilde, så den trenger en lisens. |

| Det er en ny prosessorplattform, så det er svært liten støtte for programvare- og programmeringsmiljøer. | ARM har et veldig stort nettsamfunn, som støtter biblioteker og strukturer for å hjelpe måldesignerne på forskjellige plattformer som mikroprosessorer, mikrokontrollere og også servere. |

| RISC V-baserte brikker bruker 1 watt strøm. | ARM-baserte brikker bruker under 4 watt strøm. |

| Den har et fast og variabelt ISA-kodingssystem. | Den har et fast ISA-kodingssystem. |

| Størrelsen på RISC V-instruksjonssett varierer fra 16-bit til 128-bit. | Instruksjonsstørrelsen varierer fra 16-bit til 64-bit. |

| Den inkluderer 32 registre for generelle formål og flyttall. | Den inkluderer 31 registre for generelle formål og flyttall. |

| Den har 26-enkelt presisjon flytepunkt operasjoner. | Den har 33-enkelt presisjon flytepunkt operasjoner. |

| Den har 26-dobbel presisjon flytepunkt operasjoner. | Den har 29-dobbel presisjon flytepunkt operasjoner. |

RISC V Verilog-kode

Verilog-koden for instruksjonsminnet for RISC er vist nedenfor.

// Verilog-kode for RISC-prosessor

// Verilog-kode for instruksjonsminne

modul Instruction_Memory(

input[15:0] pc,

output[15:0] instruksjon

);

reg [`col – 1:0] minne [`row_i – 1:0];

wire [3 : 0] rom_addr = pc[4 : 1];

første

begynne

$readmemb(“./test/test.prog”, minne,0,14);

slutt

tilordne instruksjon = minne[rom_addr];

endemodul

Verilog-kode for 16-biters RISC V-prosessor:

modul Risc_16_bit(

input clk

);

trådhopp,bne,beq,mem_read,mem_write,alu_src,reg_dst,mem_to_reg,reg_write;

wire[1:0] alu_op;

wire [3:0] opcode;

// Databane

Datapath_Unit DU

(

.clk(clk),

.hopp(hopp),

.frosk(frosk),

.mem_read(mem_read),

.mem_write(mem_write),

.alu_src(alu_src),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.reg_write(reg_write),

.bne(bne),

.alu_op(alu_op),

.opcode(opcode)

);

// kontrollenhet

Kontroll_Enhetskontroll

(

.opcode(opcode),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.alu_op(alu_op),

.hopp(hopp),

.bne(bne),

.frosk(frosk),

.mem_read(mem_read),

.mem_write(mem_write),

.alu_src(alu_src),

.reg_write(reg_write)

);

endemodul

Instruksjonssett

RISC V-instruksjonssettene er omtalt nedenfor.

Aritmetiske operasjoner

RISC V aritmetiske operasjoner er oppført nedenfor.

| Mnemonic | Type | Instruksjon | Beskrivelse |

| ADD rd, rs1, rs2 |

R |

Legge til | rdß rs1 + rs2 |

| SUB rd, rs1, rs2 |

R |

Trekke fra | rdß rs1 – rs2 |

| ADDI rd, rs1, imm12 |

Jeg |

Legg til umiddelbart | rdß rs1 + imm12 |

| SLT rd, rs1, rs2 |

R |

Sett mindre enn | rdß rs1 -< rs2 |

| SLTI rd, rs1, imm12 |

Jeg |

Sett mindre enn umiddelbart | rdß rs1 -< imm12 |

| SLTU rd, rs1, rs2 |

R |

Sett mindre enn usignert | rdß rs1 -< rs2 |

| SLTIU rd, rs1, imm12 |

Jeg |

Sett mindre enn umiddelbart usignert | rdß rs1 -< imm12 |

| LUI rd, imm20 |

I |

Last øvre umiddelbart | rdß imm20<<12 |

| AUIP rd,imm20 |

I |

Legg til øvre umiddelbar til PC | rdß PC+imm20<<12 |

Logiske operasjoner

RISC V logiske operasjoner er listet opp nedenfor.

| Mnemonic | Type | Instruksjon | Beskrivelse |

| OG rd, rs1, rs2 |

R |

OG | rdß rs1 og rs2 |

| ELLER rd, rs1, rs2 |

R |

ELLER | rdß rs1 | rs2 |

| XOR rd, rs1, rs2 |

R |

GRATIS | rdß rs1 ^ rs2 |

| ANDI rd, rs1, imm12 |

Jeg |

OG umiddelbar | rdß rs1 og imm2 |

| ORI rd, rs1, imm12 |

Jeg |

ELLER Umiddelbar | rdß rs1 | imm12 |

| OXRI rd, rs1, imm12 |

Jeg |

XOR umiddelbart | rdß rs1 ^ rs2 |

| SLL rd, rs1, rs2 |

R |

Skift til venstre logisk | rdß rs1 << rs2 |

| SRL rd, rs1, rs2 |

R |

Skift høyre logisk | rdß rs1 >> rs2 |

| RAS rd, rs1, rs2 |

R |

Skift til høyre aritmetikk | rdß rs1 >> rs2 |

| SLLI rd, rs1, shamt |

Jeg |

Skift til venstre logisk umiddelbart | rdß rs1 << shamt |

| SRLI rd, rs1, shamt |

Jeg |

Skift høyre logisk umiddelbart | rdß rs1 >> shamt |

| SRAI rd, rs1, shamt |

Jeg |

Skift høyre aritmetikk umiddelbart | rdß rs1 >> shamt |

Laste-/butikkdrift

RISC V laste-/lageroperasjoner er oppført nedenfor.

| Mnemonic | Type | Instruksjon | Beskrivelse |

| LD rd, imm12 (rs1) |

Jeg |

Last inn dobbeltord | rdß mem [rs1 +imm12] |

| LW rd, imm12 (rs1) |

Jeg |

Last inn ord | rdß mem [rs1 +imm12] |

| LH rd, imm12 (rs1) |

Jeg |

Last halvveis | rdß mem [rs1 +imm12] |

| LB rd, imm12 (rs1) |

Jeg |

Last inn byte | rdß mem [rs1 +imm12] |

| LWU rd, imm12 (rs1) |

Jeg |

Last inn ord usignert | rdß mem [rs1 +imm12] |

| LHU rd, imm12 (rs1) |

Jeg |

Last inn et halvt ord usignert | rdß mem [rs1 +imm12] |

| LBU rd, imm12 (rs1) |

Jeg |

Last inn byte usignert | rdß mem [rs1 +imm12] |

| SD rs2, imm12 (rs1) |

S |

Lagre dobbeltord | rs2 til mem [rs1 +imm12] |

| SW rs2, imm12 (rs1) |

S |

Lagre ord | rs2 (31:0) til mem [rs1 +imm12] |

| SH rs2, imm12 (rs1) |

S |

Lagre halvveis | rs2 (15:0) til mem [rs1 +imm12] |

| SB rs2, imm12 (rs1) |

S |

Lagre byte | rs2 (15:0) til mem [rs1 +imm12] |

| SRAI rd, rs1, shamt |

Jeg |

Skift høyre aritmetikk umiddelbart | rs2 (7:0) til mem [rs1 +imm12] |

Forgreningsoperasjoner

RISC V-forgreningsvirksomheten er oppført nedenfor.

| Mnemonic | Type | Instruksjon | Beskrivelse |

| BEQ rs1, rs2, imm12 |

SB |

Gren lik | Hvis rs1== rs2 PC ß PC+imm12 |

| BNE rs1, rs2, imm12 |

SB |

Gren ikke lik | Hvis rs1!= rs2 PC ß PC+imm12 |

| BGE rs1, rs2, imm12 |

SB |

Gren større enn eller lik | Hvis rs1>= rs2 PC ß PC+imm12 |

| BGEU rs1, rs2, imm12 |

SB |

Gren større enn eller lik usignert | Hvis rs1>= rs2 PC ß PC+imm12 |

| BLT rs1, rs2, imm12 |

SB |

Filial mindre enn | Hvis rs1< rs2 PC ß PC+imm12 |

| BLTU rs1, rs2, imm12 |

SB |

Filial mindre enn usignert | Hvis rs1< rs2 PC ß PC+imm12 <<1 |

| JAL rd, imm20 |

UJ |

Hopp og Link | rdßPC+4 PCß PC+imm20 |

| JALR rd, imm12(rs1) |

Jeg |

Hopp og Link register | rdßPC+4 PCß rs1+imm12 |

Fordeler

De fordelene med RISC V-prosessor Inkluder følgende.

- Ved å bruke RISCV kan vi spare utviklingstid, programvareutvikling, verifisering osv.

- Denne prosessoren har mange fordeler som enkelhet, åpenhet, modularitet, ren-slate-design og utvidbarhet.

- Dette støttes av flere språkkompilatorer som GCC (GNU Compiler Collection), en gratisprogramvarekompilator og gjennom Linux OS .

- Dette kan brukes av selskaper fritt på grunn av ingen royalties, ingen lisensavgifter og ingen strenger.

- RISC-V-prosessoren inkluderer ingen nye eller innovative funksjoner fordi den ganske enkelt følger etablerte prinsipper for RISC.

- I likhet med flere andre ISA-er, definerer denne prosessorspesifikasjonen ganske enkelt forskjellige instruksjonssettnivåer. Så dette inneholder 32 og 64-bits varianter samt utvidelser for å gi støtte for flyttallinstruksjoner.

- Disse er gratis, enkle, modulære, stabile, etc.

Ulemper

De ulemper med RISC V-prosessoren Inkluder følgende.

- Komplekse instruksjoner brukes ofte av kompilatorer og programmerere.

- O/p til en RISC kan endres basert på koden når påfølgende instruksjoner i en sløyfe avhenger av den tidligere instruksjonen for utførelse.

- Disse prosessorene må lagre en rekke instruksjoner raskt, noe som krever et stort cache-minnesett for å svare på instruksjonene innen rimelig tid.

- De komplette funksjonene, egenskapene og fordelene med RISC avhenger hovedsakelig av arkitekturen.

applikasjoner

De anvendelser av RISC V prosessor Inkluder følgende.

- RISC-V brukes i innebygde systemer, kunstig intelligens og maskinlæring.

- Disse prosessorene brukes i høyytelsesbaserte innebygde systemapplikasjoner.

- Denne prosessoren er egnet for bruk i enkelte felt som edge computing, AI og lagringsapplikasjoner.

- RISC-V er viktig siden det tillater mindre enhetsprodusenter å designe maskinvare uten å betale.

- Denne prosessoren lar ganske enkelt forskerne og utviklerne designe så vel som forskning med en fritt tilgjengelig ISA- eller instruksjonssettarkitektur.

- Bruksområdene til RISC V spenner fra små innebygde mikrokontrollere til stasjonære PC-er og superdatamaskiner inkludert vektorprosessorer.

Dermed er dette en oversikt over en RISC V-prosessor – arkitektur, arbeid med applikasjoner. Her er et spørsmål til deg, hva er en CISC-prosessor?