Innlegget diskuterer pinout-funksjonen og andre viktige spesifikasjoner for IC 4043. La oss lære om det komplette databladet til denne veldig interessante brikken.

Pinout-datablad av IC 4043

Teknisk sett er IC 4043 en quad set / reset (R / S) sperre med 3 logiske tilstandsutganger.

For å være mer presis har denne brikken 4 sett med innganger (som betyr 8 inngangsuttak) og 4 tilsvarende enkeltutganger.

De 4 settene med innganger består av 4 par sett / tilbakestillingsinnganger.

For hvert sett / tilbakestilling har vi en tilsvarende utgang.

Alle disse innstilte tilbakestillingsinngangene reagerer på høye logiske signaler, og skaper en bistabil effekt ved deres tilsvarende utgangspinner.

Bistable Flip / Flop

Bistable refererer til flip-flop-handling, med andre ord, en høy puls til 'sett' -inngangen gjør den tilsvarende utgangen høy fra den opprinnelige lave tilstanden, og en høy til tilbakestillingsinngangen tilbakestiller ovennevnte tilstand fra høy tilbake til lav tilstand.

Derfor, for å gjøre en tilsvarende utgang høy, må vi bruke en høy på deres 'innstilte' innganger, og for å gjøre utgangene lave igjen, trenger vi ganske enkelt å bruke en annen høy på deres tilbakestillingsinnganger.

Funksjonen til pinouts for inngang og utgang er så enkel som det.

I tillegg til dette har IC en annen interessant input pinout OE som er en vanlig output-pinout.

Still inn / tilbakestill funksjon

For å muliggjøre de ovennevnte angitte / tilbakestillingshandlingene i IC-en, bør denne OE-inngangen være koblet til logikk høy eller ganske enkelt med Vdd (supply votage).

I den ovennevnte situasjonen er utgangen tillatt med den angitte flip-flop-funksjonen.

Hvis OE-inngangen er koblet til jord, fryser utgangen og produserer en høyimpedansrespons, som verken viser en lav utgang eller en høy, snarere låser inngangen en ikke-reagerende blokkert tilstand, derav navnet 3 logisk tilstandsutgang.

Dermed kan OE-inngangen brukes til å slå av IC-funksjonen hvis det kreves for en bestemt applikasjon.

IC fungerer best med forsyningsspenninger fra 5 til 15V.

La oss oppsummere pinout-funksjoner og spesifikasjoner for IC 4043 med følgende data:

- 1Q til 4Q (Pins: 2, 9, 10, 1) 3-tilstands buffert låseutgang

- 1R til 4R (Pins: 3, 7, 11, 15) reset-inngang (aktiv HIGH)

- 1S til 4S (Pins: 4, 6, 12, 14) sett inngang (aktiv HIGH)

- OE (Pin: 5) felles utgangsaktivering

- VSS (Pin: 8) jordforsyningsspenning

- N.C. (Pin: 13) ikke tilkoblet

- VDD (Pin: 16) forsyningsspenning

Flere oppdateringer:

I disse innleggene prøver vi å forstå virkemåten til IC 4043 og IC 4044 ved å studere de forskjellige spesifikasjonene, databladet til enhetene og deres pinout-arrangement.

I utgangspunktet er begge variantene quad-cross-coupled CMOS 3-state R / S eller Reset / Set Latches. Quad betyr å ha 4 utganger som kan settes eller låses med en logikk høy gjennom et kontrollinngangssignal, eller tilbakestilles til logisk null ved et påfølgende inngangssignal.

3-tilstandsfunksjonen lar IC-ene styres ved hjelp av 3-logikk

Det grunnleggende arbeidsprinsippet til IC 4043 og IC 4044 er det samme som ovenfor, den eneste forskjellen er at IC 4043B er quad-cross-coupled 3-state HELLER IKKE Latch, og IC 4044B er quad-cross-coupled 3-state NAND Klinke.

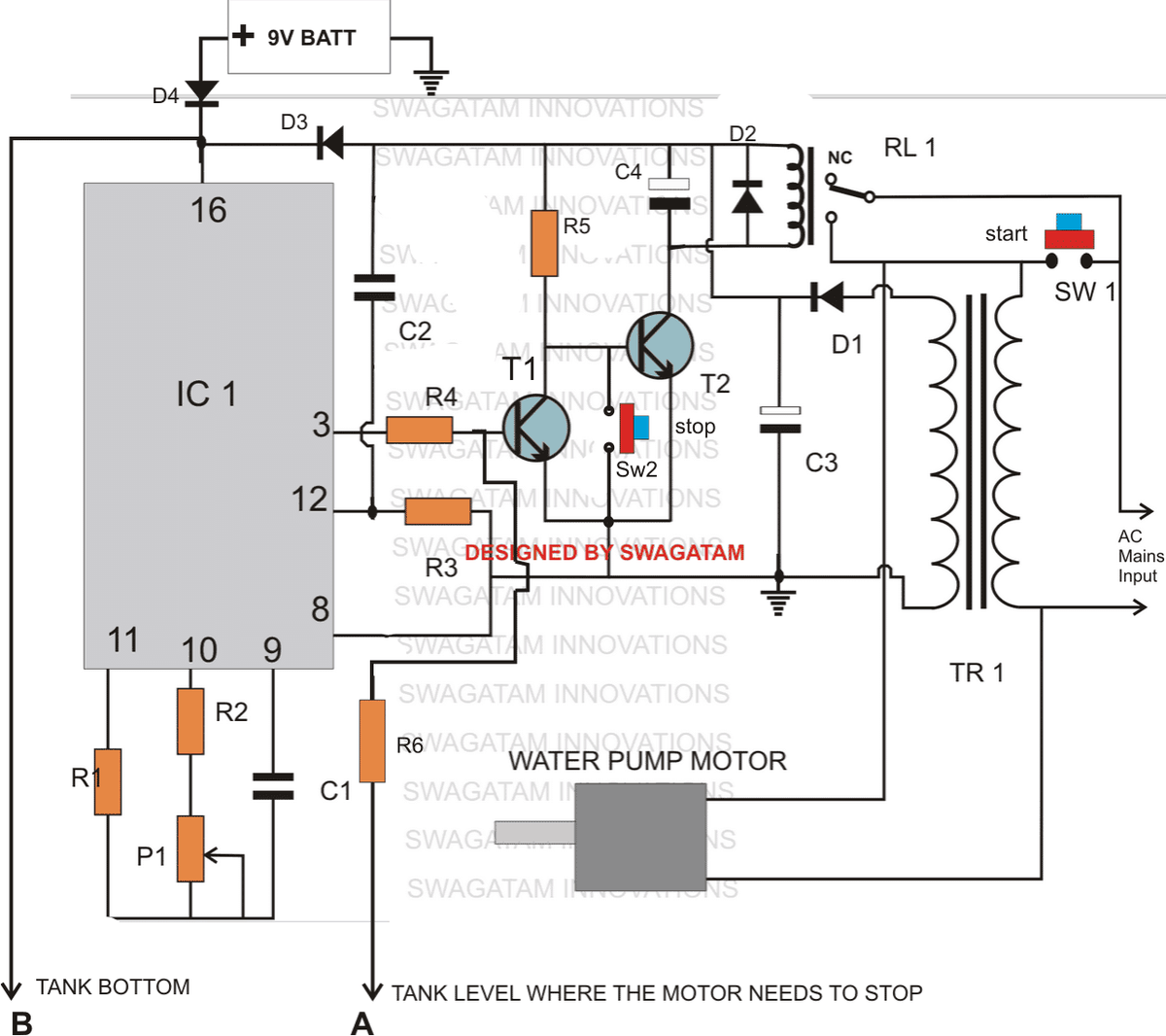

Pinout-diagram

Følgende pinouts-diagrammer over IC-ene viser den interne strukturen og pinout-detaljene til enhetene:

I diagrammene over kan vi se at hver av typene har 4 låser med en utgang og 2 individuelle RESET / SET-innganger. Funksjonen til ENABLE pin for alle SET / RESET-inngangene er identisk.

En logikk HØY ved ENABLE-pinnen gjør at sperretilstandene kan kobles til de aktuelle utgangene, en logikk lav eller 0 kobler sperretilstandene fra utgangene deres, og forårsaker en fullstendig åpen krets over utgangene.

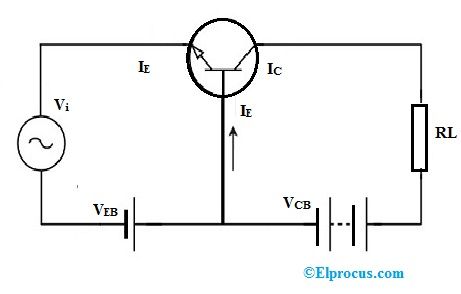

NOR Latch, NAND Latch Equivalent Logic Diagrams

De følgende diagrammene viser de tilsvarende låsene i form av NOR- og NAND-låsene, som er tilstede i hver av de 4 låsene til de enkelte IC-ene.

Som vi kan se, styres hver av låseblokkene ved hjelp av 3 logiske kontrollinnganger, nemlig SET, RESET og ENABLE, derfor er utgangen avhengig av disse 3 inngangstilstandene. Sannhetstabellen for disse tre logiske tilstandene kan læres fra følgende diagram:

I sannhetstabellen ovenfor kan fullformen til de forskjellige forkortede symbolske alfabeter forstås som gitt nedenfor: S = SET Pin R = RESET Pin E = ENABLE Pin Q = OUTPUT Pin OC = Open Circuit NC = No Change

Hovedfunksjonene til IC 4043 og IC 4044 er oppsummert nedenfor:

Praktisk grunnleggende arbeidssimulering av SET / RESET og ENABLE Pins

Arbeidsbeskrivelse

Fra ovennevnte simulerings-GIF kan vi forstå funksjonen til firkantlåsemodulene med følgende punkter:

Når SET påføres pin med en positiv forsyning, blir utgangen høy og blir låst selv om det positive potensialet blir fjernet fra SET-pinnen, som indikert av den røde lysdioden (foroverspent).

Når RESET-pinnen påføres med en positiv puls, brytes låsen, og utgangen går permanent lavt selv om den positive er fjernet fra RESET-pinnen. Dette indikeres av belysningen av den blå lysdioden.

Ovennevnte operasjoner kan bare implementeres så lenge ENABLE-pinnen på IC-en har et positivt forsyningspotensial. Når den er festet til et negativt eller jordpotensial, blir utgangen fra låsen åpen og reagerer ikke på SET / RESET-operasjonene.

Forrige: Week Day Programmable Timer Circuit Neste: IC 4033 Pinouts, datablad, applikasjon