Instruksjonssett eller instruksjonsarkitektur er strukturen til datamaskinen som gir kommandoer til datamaskinen for å veilede datamaskinen for behandling av datamanipulering. Instruksjonssett består av instruksjoner, adresseringsmodi, innfødte datatyper, registre, avbrudd, unntakshåndtering og minnearkitektur. Instruksjonssettet kan emuleres i programvare ved hjelp av en tolk eller innebygd maskinvare til prosessoren. Instruksjonsarkitektur kan betraktes som en grense mellom programvaren og maskinvaren. Klassifisering av mikrokontrollere og mikroprosessorer kan gjøres basert på RISC og CISC instruksjonsarkitektur.

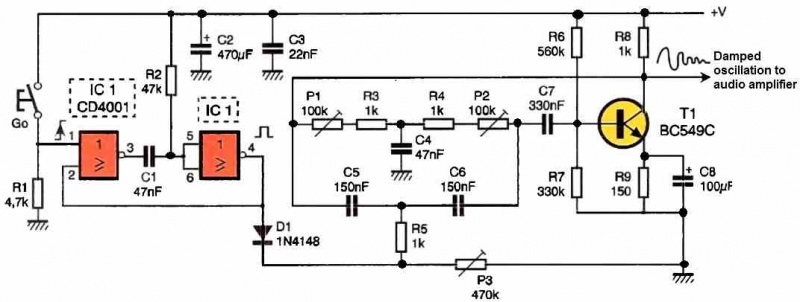

Instruksjonssett av prosessor

Instruksjonssett spesifiserer prosessorfunksjonalitet inkludert operasjoner som støttes av prosessoren, lagringsmekanismer for prosessoren, og måten å kompilere programmene til prosessoren på.

Hva er RISC og CISC?

De RISC og CISC kan utvides som følger:

RISC representerer Reduced Instruction Set Computer og

CISC representerer Complex Instruction Set Computer.

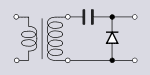

RISC (Reduced Instruction Set Computer) Arkitektur

RISC Arkitektur

De mikrokontroller arkitektur som bruker lite og svært optimalisert sett med instruksjoner kalles Reduced Instruction Set Computer eller bare kalt RISC. Det kalles også som LOAD / STORE-arkitektur.

På slutten av 1970-tallet og begynnelsen av 1980-tallet ble RISC-prosjekter primært utviklet fra Stanford, UC-Berkley og IBM. John Coke fra IBMs forskerteam utviklet RISC ved å redusere antall instruksjoner som kreves for å behandle beregninger raskere enn CISC. RISC-arkitekturen er raskere, og sjetongene som kreves for produksjon av RISC-arkitektur er også billigere sammenlignet med CISC-arkitekturen.

Typiske trekk ved RISC-arkitektur

- Rørledningsteknikk for RISC, utfører flere deler eller trinn av instruksjoner samtidig, slik at hver instruksjon på CPU-en er optimalisert. Derfor har RISC-prosessorene Clock per Instruction of one cycle, og dette kalles som One Cycle Execution.

- Det optimaliserer bruk av register med mer antall registre i RISC og mer antall interaksjoner i minnet kan forhindres.

- Enkle adresseringsmodi, til og med kompleks adressering kan gjøres ved hjelp av aritmetikk OG / ELLER logiske operasjoner .

- Det forenkler kompileringsdesignet ved å bruke identiske register for generelle formål som gjør at ethvert register kan brukes i alle sammenhenger.

- For effektiv bruk av registrene og optimalisering av rørledningsbruken er det nødvendig med redusert instruksjonssett.

- Antall bits som brukes til opkoden reduseres.

- Generelt er det 32 eller flere registre i RISC.

Fordeler med RISC-prosessorarkitektur

- På grunn av det lille settet med instruksjoner fra RISC, kan språkkompilatorer på høyt nivå produsere mer effektiv kode.

- RISC gir frihet til å bruke plassen på mikroprosessorer på grunn av sin enkelhet.

- I stedet for å bruke Stack, bruker mange RISC-prosessorer registrene for å sende argumenter og holde de lokale variablene.

- RISC-funksjoner bruker bare noen få parametere, og RISC-prosessorer kan ikke bruke anropsinstruksjonene, og bruker derfor instruksjoner med fast lengde som er enkle å pipeline.

- Operasjonshastigheten kan maksimeres og utførelsestiden kan minimeres.

- Svært mindre antall instruksjonsformater (mindre enn fire), noen få instruksjoner (rundt 150) og noen få adresseringsmodi (mindre enn fire) er nødvendig.

Ulemper med RISC-prosessorarkitektur

- Med økningen i lengden på instruksjonene øker kompleksiteten for RISC-prosessorer å utføre på grunn av sin karaktersyklus per instruksjon.

- Ytelsen til RISC-prosessorene avhenger hovedsakelig av kompilatoren eller programmereren, da kompilatorens kunnskap spiller en viktig rolle mens du konverterer CISC-koden til en RISC-kode, og derfor avhenger kvaliteten på den genererte koden av kompilatoren.

- Mens du planlegger CISC-koden til en RISC-kode, betegnet som en kodeutvidelse, vil den øke størrelsen. Og kvaliteten på denne kodeutvidelsen vil igjen avhenge av kompilatoren, og også av maskinens instruksjonssett.

- Første nivå cache til RISC-prosessorene er også en ulempe med RISC, der disse prosessorene har store minnebuffere på selve brikken. For å mate instruksjonene, krever de veldig raske minnesystemer .

CISC (Complex Instruction Set Computer) Arkitektur

Hovedintensjonen med CISC-prosessorarkitekturen er å fullføre oppgaven ved å bruke færre antall samlebånd. For dette formålet er prosessoren bygget for å utføre en rekke operasjoner. Kompleks instruksjon blir også betegnet som MULT, som fungerer minnebanker på en datamaskin direkte uten å få kompilatoren til å utføre lagrings- og lastefunksjoner.

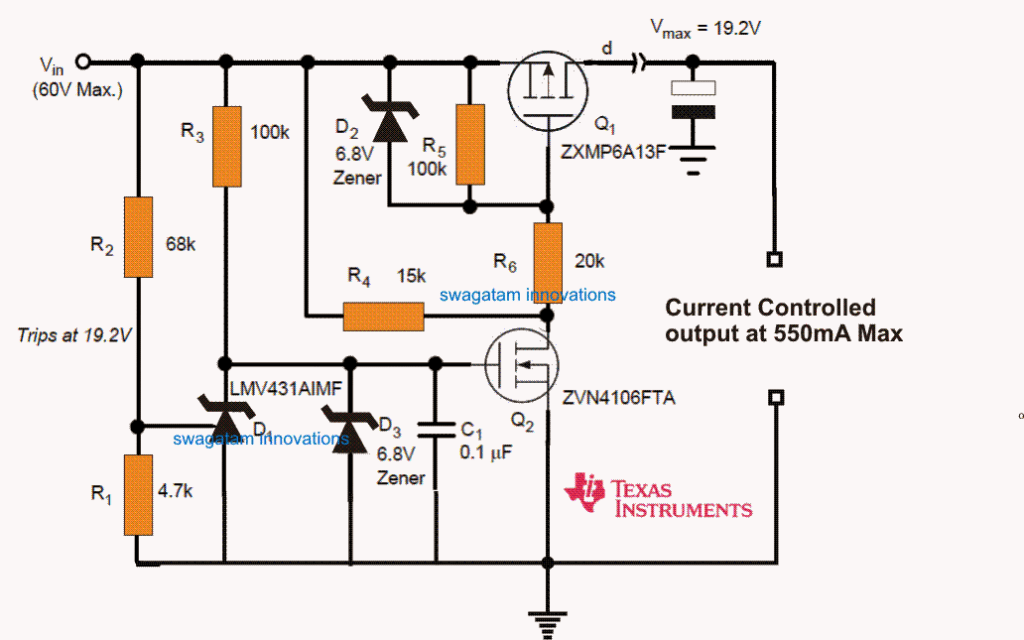

CISC Arkitektur

Funksjoner av CISC Architecture

- For å forenkle dataarkitekturen støtter CISC mikroprogrammering.

- CISC har flere forhåndsdefinerte instruksjoner som gjør språk på høyt nivå enkle å designe og implementere.

- CISC består av færre antall registre og mer antall adresseringsmodi, vanligvis 5 til 20.

- CISC-prosessor tar varierende syklustid for utføring av instruksjoner - sykluser med flere klokker.

- På grunn av det komplekse instruksjonssettet til CISC er rørledningsteknikken veldig vanskelig.

- CISC består av flere antall instruksjoner, vanligvis fra 100 til 250.

- Spesielle instruksjoner brukes svært sjelden.

- Operandene i minnet manipuleres av instruksjoner.

Fordeler med CISC-arkitektur

- Hver maskinspråkinstruksjon er gruppert i en mikrokodeinstruksjon og utført tilsvarende, og lagres deretter innebygd i minnet til hovedprosessoren, betegnet som implementering av mikrokoder.

- Ettersom mikrokodeminnet er raskere enn hovedminnet, kan mikrokodeinstruksjonssettet implementeres uten betydelig hastighetsreduksjon i forhold til hard kablet implementering.

- Hele nye instruksjonssett kan håndteres ved å endre mikroprogrammets design.

- CISC, antall instruksjoner som kreves for å implementere et program kan reduseres ved å bygge rike instruksjonssett og kan også gjøres for å bruke langsomt hovedminne mer effektivt.

- På grunn av det overordnede settet med instruksjoner som består av alle tidligere instruksjoner, gjør dette mikrokoding enkel.

Ulemper med CISC

- Mengden klokketid som er tatt av forskjellige instruksjoner vil være forskjellig - på grunn av dette bremser maskinens ytelse.

- Instruksjonssettets kompleksitet og chipmaskinvaren øker ettersom hver nye versjon av prosessoren består av en delmengde av tidligere generasjoner.

- Bare 20% av de eksisterende instruksjonene brukes i en typisk programmeringshendelse, selv om det finnes mange spesialiserte instruksjoner som ikke engang brukes ofte.

- Betingelseskodene settes av CISC-instruksjonene som en bivirkning av hver instruksjon som tar tid for denne innstillingen - og når den påfølgende instruksjonen endrer tilstandskodebitene, må kompilatoren undersøke tilstandskodebitene før dette skjer.

RISC vs. CISC

- Avfallssyklusene kan forhindres av programmereren ved å fjerne den unødvendige koden i RISC, men mens du bruker CISC-koden, fører det til å kaste bort sykluser på grunn av ineffektiviteten til CISC.

- I RISC er hver instruksjon ment for å utføre en liten oppgave slik at, for å utføre en kompleks oppgave, brukes flere små instruksjoner sammen, mens bare få instruksjoner er nødvendige for å gjøre den samme oppgaven ved hjelp av CISC - da den er i stand til å utføre en kompleks oppgave da instruksjonene ligner på en høyspråklig kode.

- CISC brukes vanligvis til datamaskiner mens RISC brukes til smarttelefoner, nettbrett og andre elektroniske enheter.

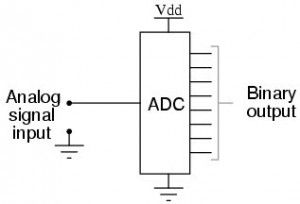

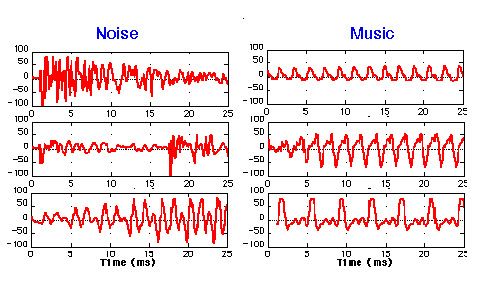

Følgende figur viser flere forskjeller mellom RISC og CISC

RISC vs. CISC

Dermed diskuterer denne artikkelen om RISC og CISC arkitekturer funksjonene til RISC og CISC prosessorer arkitektur fordeler og ulemper med RISC og CISC, og forskjeller mellom RISC og CISC arkitekturer med en kort ide. For mer informasjon om RISC- og CISC-arkitekturen, vennligst legg inn spørsmålene dine ved å kommentere nedenfor.

Fotokreditter:

- Instruksjonssett av prosessor av arstechnica

- RISC Architecture av LSI-konkurranse

- RISC vs. CISC av csarassignment