I dette innlegget skal vi forstå omfattende om hva logiske porter er og hvordan det fungerer. Vi vil ta en titt på den grunnleggende definisjonen, symbolet, sannhetstabellen, Multi-inngangsporter, vi vil også konstruere transistorbaserte gateekvivalenter, og til slutt vil vi ta en oversikt over forskjellige relevante CMOS IC-er.

Hva er Logic Gates

En logisk gate i en elektronisk krets kan uttrykkes som en fysisk enhet representert gjennom en boolsk funksjon.

Med andre ord er en logisk gate designet for å utføre en logisk funksjon ved bruk av enkle eller flere binære innganger og for å generere en enkelt binær utgang.

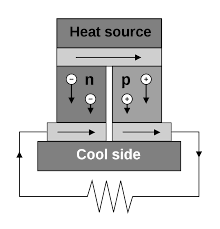

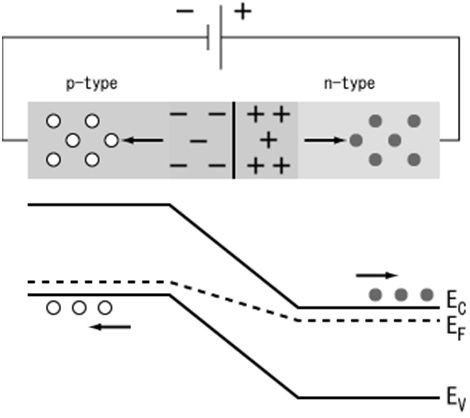

Elektroniske logiske porter er fundamentalt konfigurert og implementert ved hjelp av halvlederblokker eller elementer som dioder eller transistorer som fungerer som PÅ / AV-brytere med et veldefinert koblingsmønster. Logiske porter letter kaskaden av portene slik at det lett muliggjør sammensetning av boolske funksjoner, noe som gjør det mulig å lage fysiske modeller av all boolsk logikk. Dette muliggjør ytterligere algoritmer og matematikk som kan skrives ved hjelp av boolsk logikk.

Logiske kretser kan benytte halvlederelementer i rekkevidden av multipleksere, registre, aritmetiske logiske enheter (ALUer) og dataminne og til og med mikroprosessorer, som involverer så høyt som 100-tallet av millioner av logiske porter. I dagens implementering finner du for det meste felt-effekt transistorer (FET), som brukes til å produsere logiske porter, et godt eksempel er en metall-oksid-halvleder felt-effekt transistorer eller MOSFET.

La oss begynne opplæringen med logikk OG porter.

Hva er Logic “AND” Gate?

Det er en elektronisk port, hvis utgang blir 'høy' eller '1' eller 'sann' eller gir ut et 'positivt signal' når alle inngangene til OG-portene er 'høye' eller '1' eller 'sanne' eller ' positivt signal ”.

For eksempel: Si i en AND-port med ‘n’ antall innganger, hvis alle inngangene er “høye” blir utgangen “høy”. Selv om en inngang er 'LAV' eller '0' eller 'falsk' eller 'negativt signal', blir utgangen 'LAV' eller '0' eller 'falsk' eller gir ut et 'negativt signal'.

Merk:

Uttrykket “Høy”, “1”, “positivt signal”, “sant” er egentlig det samme (Positivt signal er batteriets eller strømforsyningens positive signal).

Begrepet 'LAV', '0', 'negativt signal', 'falsk' er i det vesentlige det samme (negativt signal er batteriets eller strømforsyningens negative signal).

Illustrasjon av Logic AND gate symbol:

Her er 'A' og 'B' de to inngangene, og 'Y' blir sendt ut.

Det boolske uttrykket for logikk OG gate: Utgangen 'Y' er multiplikasjon av de to inngangene 'A' og 'B'. (A.B) = Y.

Den boolske multiplikasjonen er betegnet med en prikk (.)

Hvis 'A' er '1' og 'B' er '1' er utgangen (A.B) = 1 x 1 = '1' eller 'høy'

Hvis ‘A’ er ‘0’ og ‘B’ er ‘1’ er utgangen (A.B) = 0 x 1 = ‘0’ eller “Lav”

Hvis ‘A’ er ‘1’ og ‘B’ er ‘0’ er utgangen (A.B) = 1 x 0 = ‘0’ eller “Lav”

Hvis 'A' er '0' og 'B' er '0' er utgangen (A.B) = 0 x 0 = '0' eller 'Lav'

Ovennevnte forhold er forenklet i sannhetstabellen.

Sannhetstabell (to innganger):

| A (inngang) | B (INNGANG) | Y (utgang) |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

3-inngangs 'AND' -port:

Illustrasjon av 3 inngang OG port:

Logiske OG-porter kan ha ‘n’ antall innganger, noe som betyr at den kan ha mer enn to innganger (Logiske OG-porter vil ha minst to innganger og alltid en utgang).

For en inngang med 3 innganger blir den boolske ligningen slik: (A.B.C) = Y, på samme måte for 4 innganger og over.

Sannhetstabell for 3 inngangslogikk OG gate:

| A (INNGANG) | B (INNGANG) | C (INNGANG) | Y (UTGANG) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Multi-inngangslogikk OG porter:

Kommersielt tilgjengelige Logic AND-porter er bare tilgjengelig i 2, 3 og 4 innganger. Hvis vi har mer enn 4 innspill, må vi kaskade portene.

Vi kan ha seks inngangslogikk OG porter ved å kaskade de 2 inngang OG Porter som følger:

Nå blir den boolske ligningen for kretsen ovenfor Y = (A.B). (C.D). (E.F)

Likevel gjelder alle de nevnte logiske reglene for kretsen ovenfor.

Hvis du bare skal bruke 5 innganger fra de ovennevnte 6 innganger OG porter, kan vi koble til en mottaksmotstand på en hvilken som helst pin, og nå blir den 5 inngang OG port.

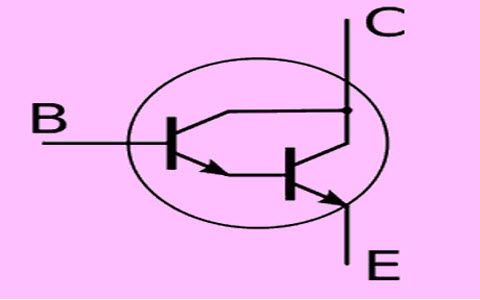

Transistorbasert to inngangslogikk OG gate:

Nå vet vi hvordan en logikk OG gate fungerer, la oss konstruere en 2 inngang OG gate ved hjelp av to NPN-transistorer. De logiske IC-ene er konstruert på nesten samme måte.

To skjermbilder med transistor OG port:

Ved utgangen “Y” kan du koble til en LED hvis utgangen er høy, vil LED-en lyse (LED + Ve-terminal på “Y” med 330 ohm motstand og negativ til GND).

Når vi bruker høysignal til basen til de to transistorene, slås begge transistorene PÅ, + 5V-signalet vil være tilgjengelig på senderen til T2, og dermed blir utgangen høy.

Hvis en av transistoren er AV, vil ingen positiv spenning være tilgjengelig på senderen av T2, men på grunn av 1K-trekkmotstanden vil den negative spenningen være tilgjengelig på utgangen, så utgangen blir referert til som lav.

Nå vet du hvordan du konstruerer din egen logikk OG gate.

Quad AND gate IC 7408:

Hvis du vil kjøpe logikk OG gate fra markedet, vil du komme i konfigurasjonen ovenfor.

Den har 14 pinner, pin nr. 7 og pin nr. 14 er henholdsvis GND og Vcc. Den drives på 5V.

Forplantningsforsinkelse:

Forplantningsforsinkelse er tiden det tar for produksjonen å endre seg fra LAV til HØY og omvendt.

Forplantningsforsinkelsen fra LAV til HØY er 27 nanosekunder.

Forplantningsforsinkelsen fra HIGH til LOW er 19 nanosekunder.

Andre vanlige tilgjengelige 'AND' gate ICer:

• 74LS08 Quad 2-inngang

• 74LS11 Triple 3-inngang

• 74LS21 Dobbel 4-inngang

• CD4081 Quad 2-inngang

• CD4073 Triple 3-inngang

• CD4082 Dual 4-inngang

Du kan alltid se datablad for IC-ene over for mer informasjon.

Hvordan logikk “Exclusive NOR” Gate Funksjon

I dette innlegget skal vi utforske om logikken 'Ex-NOR' gate eller Exclusive-NOR gate. Vi tar en titt på den grunnleggende definisjonen, symbolet, sannhetstabellen, Ex-NOR-ekvivalent krets, Ex-NOR-realisering ved hjelp av logikk NAND-porter og til slutt vil vi ta oversikt over quad 2 inngang Ex-OR gate IC 74266.

Hva er 'Exclusive NOR' gate?

Det er en elektronisk port, hvis utgang blir 'høy' eller '1' eller 'sann' eller gir ut et 'positivt signal' når inngangene er like antall logiske '1s' (eller 'sann' eller 'høy' eller ' positivt signal ”).

For eksempel: Si en eksklusiv NOR-gate med ‘n’ antall innganger, hvis inngangene er logiske “HIGH” med 2 eller 4 eller 6 innganger (jevnt antall innganger “1s”) blir utgangen “HIGH”.

Selv om vi ikke bruker logikk “høy” på inngangspinnene (dvs. null antall logiske “HØY” og all logikk “LAV”), er fortsatt “null” et partall som utgangen blir “HØY”.

Hvis antall logiske '1s' som brukes, er ODD, blir utgangen 'LAV' (eller '0' eller 'falsk' eller 'negativt signal').

Dette er motsatt av logikk “Exclusive OR” gate der utgangen blir “HIGH” når inngangene er ODD antall logiske “1s”.

Merk:

Uttrykket “Høy”, “1”, “positivt signal”, “sant” er egentlig det samme (Positivt signal er batteriets eller strømforsyningens positive signal).

Begrepet 'LAV', '0', 'negativt signal', 'falsk' er i det vesentlige det samme (negativt signal er batteriets eller strømforsyningens negative signal).

Illustrasjon av Logic “Exclusive NOR” gate:

“Eksklusiv NOR” gate ekvivalent krets:

Ovennevnte er ekvivalent krets for logikk Ex-NOR, som i utgangspunktet er en kombinasjon av logisk “Exclusive OR” gate og logisk “NOT” gate.

Her er 'A' og 'B' de to inngangene, og 'Y' blir sendt ut.

Det boolske uttrykket for logikk Ex-NOR gate: Y = (AB) ̅ + AB.

Hvis ‘A’ er ‘1’ og ‘B’ er ‘1’ er utgangen ((AB) ̅ + AB) = 0 + 1 = ‘1’ eller “HIGH”

Hvis ‘A’ er ‘0’ og ‘B’ er ‘1’ er utgangen ((AB) ̅ + AB) = 0 + 0 = ‘0’ eller “LAV”

Hvis ‘A’ er ‘1’ og ‘B’ er ‘0’ er utgangen ((AB) ̅ + AB) = 0 + 0 = ‘0’ eller “LAV”

Hvis ‘A’ er ‘0’ og ‘B’ er ‘0’ er utgangen ((AB) ̅ + AB) = 1 + 1 = ‘1’ eller “HIGH”

Ovennevnte forhold er forenklet i sannhetstabellen.

Sannhetstabell (to innganger):

| A (inngang) | B (INNGANG) | Y (utgang) |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

3 innganger eksklusiv NOR Gate:

Illustrasjon av 3 inngangs Ex-NOR gate:

Sannhetstabell for 3 inngangslogikk EX-OR-gate:

| A (INNGANG) | B (INNGANG) | C (INNGANG) | Y (UTGANG) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

For 3-inngangs Ex-NOR-port blir den boolske ligningen: A ̅ (BC) ̅ + ABC ̅ + AB ̅C + A ̅BC.

Logikken 'Ex-NOR' gate er ikke en grunnleggende logisk gate, men en kombinasjon av forskjellige logiske porter. Ex-NOR-porten kan realiseres ved hjelp av logiske 'ELLER' -porter, logiske 'OG' -port og logiske 'NAND' -port som følger:

Tilsvarende krets for “Exclusive NOR” gate:

Ovennevnte design har stor ulempe, vi trenger 3 forskjellige logiske porter for å lage en Ex-NOR-port. Men vi kan overvinne dette problemet ved å implementere Ex-NOR gate med bare logiske 'NAND' porter, dette er også økonomisk å lage.

Eksklusiv NOR gate ved hjelp av NAND gate:

Eksklusive NOR-porter brukes til å utføre kompliserte databehandlingsoppgaver som aritmetiske operasjoner, binære addere, binær subtraksjon, paritetskontroll og de brukes som digitale komparatorer.

Logic Exclusive-NOR Gate IC 74266:

Hvis du vil kjøpe logisk Ex-NOR gate fra markedet, vil du komme i DIP-konfigurasjonen ovenfor.

Den har 14 pinner, pin nr. 7 og pin nr. 14 er henholdsvis GND og Vcc. Den drives på 5V.

Forplantningsforsinkelse:

Forplantningsforsinkelse er tiden det tar for utgangen å endre seg fra LAV til HØY og omvendt etter å ha gitt innspill.

Forplantningsforsinkelsen fra LAV til HØY er 23 nanosekunder.

Forplantningsforsinkelsen fra HØY til LAV er 23 nanosekunder.

Vanlig tilgjengelige 'EX-NOR' gate ICer:

74LS266 Quad 2-inngang

CD4077 Quad 2-inngang

Hvordan NAND Gate fungerer

I forklaringen nedenfor skal vi utforske om digital logikk NAND gate. Vi vil ta en titt på grunnleggende definisjon, symbol, sannhetstabell, Multi input NAND gate, vi skal konstruere transistorbasert 2 inngangs NAND gate, forskjellige logiske porter som bare bruker NAND gate og til slutt vil vi ta en oversikt over NAND gate IC 7400.

Hva er Logic “NAND” Gate?

Det er en elektronisk gate, hvis utgang blir 'LAV' eller '0' eller 'falsk' eller gir ut et 'negativt signal' når alle inngangene til NAND-portene er 'høye' eller '1' eller 'sanne' eller ' positivt signal ”.

For eksempel: Si en NAND-gate med ‘n’ antall innganger, hvis alle inngangene er “høye” blir utgangen “LAV”. Selv om en inngang er 'LAV' eller '0' eller 'falsk' eller 'negativt signal', blir utgangen 'HØY' eller '1' eller 'sann' eller gir et 'positivt signal'.

Merk:

Uttrykket “Høy”, “1”, “positivt signal”, “sant” er egentlig det samme (Positivt signal er batteriets eller strømforsyningens positive signal).

Begrepet 'LAV', '0', 'negativt signal', 'falsk' er i det vesentlige det samme (negativt signal er batteriets eller strømforsyningens negative signal).

Illustrasjon av Logic NAND gate symbol:

Her er 'A' og 'B' de to inngangene, og 'Y' blir sendt ut.

Dette symbolet er “OG” -port med inversjon “o”.

Logisk 'NAND' Gate-ekvivalent krets:

Den logiske NAND-porten er kombinasjonen av logisk 'OG' -port og logisk 'IKKE' -port.

Det boolske uttrykket for logisk NAND-gate: Utgangen 'Y' er komplementær multiplikasjon av de to inngangene 'A' og 'B'. Y = ((A.B) ̅)

Den boolske multiplikasjonen er betegnet med en prikk (.) Og den komplementære (inversjonen) er representert med en stolpe (-) over en bokstav.

Hvis ‘A’ er ‘1’ og ‘B’ er ‘1’ er utgangen ((A.B) ̅) = (1 x 1) ̅ = ‘0’ eller “LAV”

Hvis 'A' er '0' og 'B' er '1' er utgangen ((A.B) ̅) = (0 x 1) ̅ = '1' eller 'HIGH'

Hvis ‘A’ er ‘1’ og ‘B’ er ‘0’ er utgangen ((A.B) ̅) = (1 x 0) ̅ = ‘1’ eller “HIGH”

Hvis 'A' er '0' og 'B' er '0', er utgangen ((A.B) ̅) = (0 x 0) ̅ = '1' eller 'HIGH'

Ovennevnte forhold er forenklet i sannhetstabellen.

Sannhetstabell (to innganger):

| A (inngang) | B (INNGANG) | Y (utgang) |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

3-inngangs 'NAND' -port:

Illustrasjon av NAND-port med 3 innganger:

Logiske NAND-porter kan ha 'n' antall innganger, noe som betyr at de kan ha mer enn to innganger

(Logiske NAND-porter vil ha minst to innganger og alltid en utgang).

For en NAND-port med 3 innganger blir den boolske ligningen slik: ((A.B.C) ̅) = Y, tilsvarende for 4 innganger og over.

Sannhetstabellfor 3 inngangs logikk NAND gate:

| A (INNGANG) | B (INNGANG) | C (INNGANG) | Y (UTGANG) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Multi Input Logic NAND-porter:

Kommersielt tilgjengelige Logic NAND-porter er bare tilgjengelig i 2, 3 og 4 innganger. Hvis vi har mer enn 4 innspill, må vi kaskade portene.

For eksempel kan vi ha fire inngangslogiske NAND-gate ved å kaskade 5 to NAND-porter som følger:

Nå blir den boolske ligningen for kretsen ovenfor Y = ((A.B.C.D) ̅)

Likevel gjelder alle de nevnte logiske reglene for kretsen ovenfor.

Hvis du bare skal bruke 3 innganger fra de ovennevnte NAND-portene på 4 innganger, kan vi koble en trekkmotstand til en hvilken som helst pin, og nå blir den NAND-gate med 3 innganger.

Transistorbasert to-inngangs logisk NAND-gate:

Nå vet vi hvordan en logisk NAND-gate fungerer, la oss konstruere en NAND-gate med 2 innganger ved hjelp av to

NPN-transistorer. De logiske IC-ene er konstruert på nesten samme måte.

To transistor NAND gate skjematisk:

Ved utgangen “Y” kan du koble til en LED hvis utgangen er høy, lysdioden vil lyse (LED + Ve-terminal på “Y” med 330 ohm motstand og negativ til GND).

Når vi bruker høysignal til basen til de to transistorene, slås begge transistorene PÅ, bakkesignalet vil være tilgjengelig på samleren til T1, og dermed blir utgangen “LAV”.

Hvis en av transistoren er AV, dvs. å bruke et 'LAV' signal til basen, vil det ikke være noe bakkesignal tilgjengelig ved samleren av T1, men på grunn av 1K opptrekksmotstand vil det positive signalet være tilgjengelig ved utgangen og utgangen blir 'HØY'.

Nå vet du hvordan du lager din egen logiske NAND-gate.

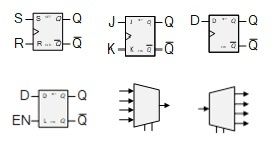

Ulike logiske porter ved bruk av NAND gate:

NAND-porten er også kjent som 'universal logic gate' fordi vi kan lage hvilken som helst boolsk logikk med denne enkeltporten. Dette er en fordel for å fremstille IC-er med forskjellige logiske funksjoner, og det er økonomisk å lage en enkelt gate.

I skjemaene ovenfor vises bare 3 typer porter, men vi kan lage hvilken som helst boolsk logikk.

Quad NAND gate IC 7400:

Hvis du vil kjøpe en logisk NAND-gate fra markedet, kommer du i DIP-konfigurasjonen ovenfor.

Den har 14 pinner, pin nr. 7 og pin nr. 14 er henholdsvis GND og Vcc. Den drives på 5V.

Forplantningsforsinkelse:

Forplantningsforsinkelse er tiden det tar for utgangen å endre seg fra LAV til HØY og omvendt etter å ha gitt en inngang.

Forplantningsforsinkelsen fra LAV til HØY er 22 nanosekunder.

Forplantningsforsinkelsen fra HØY til LAV er 15 nanosekunder.

Det er flere andre NAND gate ICer tilgjengelig:

- 74LS00 Quad 2-inngang

- 74LS10 Triple 3-inngang

- 74LS20 Dobbel 4-inngang

- 74LS30 Enkelt 8-inngang

- CD4011 Quad 2-inngang

- CD4023 Triple 3-inngang

- CD4012 Dobbel 4-inngang

Hvordan NOR Gate fungerer

Her skal vi utforske om digital logikk NOR gate. Vi tar en titt på den grunnleggende definisjonen, symbolet, sannhetstabellen, Multi input NOR gate, vi skal konstruere transistorbasert 2 input NOR gate, forskjellige logiske porter som bare bruker NOR gate og til slutt vil vi ta en oversikt over NOR gate IC 7402.

Hva er Logic “NOR” Gate?

Det er en elektronisk port, hvis utgang blir “HØY” eller “1” eller “sann” eller gir et “positivt signal” når alle inngangene til NOR-portene er “LAV” eller “0” eller “falske” eller “ negativt signal ”.

For eksempel: Si en NOR-gate med ‘n’ antall innganger, hvis alle inngangene er “LAV” blir utgangen “HØY”. Selv om en inngang er “HIGH” eller “1” eller “true” eller “positive signal”, blir utgangen “LOW” eller “0” eller “false” eller gir et “negativt signal”.

Merk:

Uttrykket “Høy”, “1”, “positivt signal”, “sant” er egentlig det samme (Positivt signal er batteriets eller strømforsyningens positive signal).

Begrepet 'LAV', '0', 'negativt signal', 'falsk' er i det vesentlige det samme (negativt signal er batteriets eller strømforsyningens negative signal).

Illustrasjon av Logic NOR gate symbol:

Her er 'A' og 'B' de to inngangene, og 'Y' blir sendt ut.

Dette symbolet er “ELLER” -porten med inversjon “o”.

Logisk 'NOR' Gate-ekvivalent krets:

Den logiske NOR-porten er kombinasjonen av logisk 'ELLER' -port og logisk 'IKKE' -port.

Det boolske uttrykket for logisk NOR gate: Utgangen ‘Y’ er komplementær tillegg av de to inngangene ‘A’ og ‘B’. Y = ((A + B) ̅)

Det boolske tillegget er betegnet med (+) og det komplementære (inversjon) er representert med en strek (-) over en bokstav.

Hvis ‘A’ er ‘1’ og ‘B’ er ‘1’ er utgangen ((A + B) ̅) = (1+ 1) ̅ = ‘0’ eller “LAV”

Hvis ‘A’ er ‘0’ og ‘B’ er ‘1’ er utgangen ((A + B) ̅) = (0+ 1) ̅ = ‘0’ eller “LAV”

Hvis ‘A’ er ‘1’ og ‘B’ er ‘0’ er utgangen ((A + B) ̅) = (1+ 0) ̅ = ‘0’ eller “LAV”

Hvis ‘A’ er ‘0’ og ‘B’ er ‘0’ er utgangen ((A + B) ̅) = (0+ 0) ̅ = ‘1’ eller “HIGH”

Ovennevnte forhold er forenklet i sannhetstabellen.

Sannhetstabell (to innganger):

| A (inngang) | B (INNGANG) | Y (utgang) |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

3-inngang “NOR” -port:

Illustrasjon av 3 inngangs NOR gate:

Logiske NOR-porter kan ha ‘n’ antall innganger, noe som betyr at det kan ha mer enn to innganger (Logiske NOR-porter vil ha minst to innganger og alltid en utgang).

For en 3-inngangs NOR-gate blir den boolske ligningen slik: ((A + B + C) ̅) = Y, på samme måte for 4 innganger og over.

Sannhetstabell for 3 inngangs logikk NOR gate:

| A (INNGANG) | B (INNGANG) | C (INNGANG) | Y (UTGANG) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

Multi Input Logic NOR-porter:

Kommersielt tilgjengelige Logic NOR-porter er bare tilgjengelig i 2, 3 og 4 innganger. Hvis vi har mer enn 4 innspill, må vi kaskade portene.

For eksempel kan vi ha fire inngangslogiske NOR gate ved å kaskade 5 to inngang NOR porter som følger:

Nå blir den boolske ligningen for kretsen ovenfor Y = ((A + B + C + D) ̅)

Likevel gjelder alle de nevnte logiske reglene for kretsen ovenfor.

Hvis du bare skal bruke 3 innganger fra de ovennevnte 4 inngangene NOR-porten, kan vi koble en nedtrekkbar motstand til hvilken som helst av pinnen, og nå blir den 3 inngangs NOR-porten.

Transistorbasert to inngangs Logic NOR gate:

Nå vet vi hvordan en logisk NOR-gate fungerer, la oss konstruere en 2-inngangs NOR-gate ved hjelp av to NPN-transistorer. De logiske IC-ene er konstruert på nesten samme måte.

To transistor NOR gate skjematisk:

Ved utgangen “Y” kan du koble til en LED hvis utgangen er høy, lysdioden vil lyse (LED + Ve-terminal på “Y” med 330 ohm motstand og negativ til GND).

Når vi bruker “HIGH” -signal til basen til de to transistorene, slås begge transistorene PÅ og bakkesignalet vil være tilgjengelig på samleren til T1 og T2, og dermed blir utgangen “LAV”.

Hvis vi bruker “HIGH” på en av transistoren, vil fortsatt det negative signalet være tilgjengelig på utgangen, noe som får utgangen til “LAV”.

Hvis vi bruker 'LAV' signal på basen av to transistorer, slås begge AV, men på grunn av opptrekksmotstanden blir utgangen 'HIGH'.

Nå vet du hvordan du lager din egen logiske NOR gate.

Ulike logiske porter ved bruk av NOR gate:

MERKNAD: NAND og NOR er de to portene, ellers kjent som universale porter.

NOR-porten er også en 'universell logikkport' fordi vi kan lage hvilken som helst boolsk logikk med denne enkle porten. Dette er en fordel for å produsere IC-er med forskjellige logiske funksjoner, og det er økonomisk å produsere en enkelt gate, dette er det samme for NAND-porten.

I de ovennevnte skjemaene vises bare 3 typer porter, men vi kan lage alle boolske logikker.

Quad NOR gate IC 7402:

Hvis du vil kjøpe en logisk NOR-gate fra markedet, kommer du i DIP-konfigurasjonen ovenfor.

Den har 14 pinner, pin nr. 7 og pin nr. 14 er henholdsvis GND og Vcc. Den drives på 5V.

Forplantningsforsinkelse:

Forplantningsforsinkelse er tiden det tar for utgangen å endre seg fra LAV til HØY og omvendt etter å ha gitt en inngang.

Forplantningsforsinkelsen fra LAV til HØY er 22 nanosekunder.

Forplantningsforsinkelsen fra HØY til LAV er 15 nanosekunder.

Det er flere andre NOR gate ICer tilgjengelig:

- 74LS02 Quad 2-inngang

- 74LS27 Triple 3-inngang

- 74LS260 Dobbel 4-inngang

- CD4001 Quad 2-inngang

- CD4025 Triple 3-inngang

- CD4002 Dual 4-inngang

Logikk IKKE Gate

I dette innlegget skal vi utforske om logikk 'IKKE' gate. Vi vil lære om dens grunnleggende definisjon, symbol, sannhetstabell, NAND- og NOR-gateekvivalenter, Schmitt-omformere, Schmitt IKKE gate-oscillator, IKKE gate ved hjelp av transistor, og til slutt vil vi ta en titt på logikk IKKE gate-inverter IC 7404.

Før vi begynner å se på detaljene i logisk NOT gate, som også kalles digital omformer, må man ikke forveksle med 'Power inverters' som brukes i solenergi eller reservestrømforsyninger hjemme eller på kontoret.

Hva er Logic “NOT” Gate?

Det er en enkelt inngangs- og enkeltutgangslogisk gate hvis utgang er et supplement til inngangen.

Ovennevnte definisjon sier at hvis inngangen er “HIGH” eller “1” eller “true” eller “positive signal” vil utgangen være “LOW” eller “0” eller “false” eller “negative signal”.

Hvis inngangen er 'LAV' eller '0' eller 'falsk' eller 'negativt signal' vil utgangen bli invertert til 'HØY' eller '1' eller 'sann' eller 'positiv signal'

Merk:

Uttrykket “Høy”, “1”, “positivt signal”, “sant” er egentlig det samme (Positivt signal er batteriets eller strømforsyningens positive signal).

Begrepet 'LAV', '0', 'negativt signal', 'falsk' er i det vesentlige det samme (negativt signal er batteriets eller strømforsyningens negative signal).

Illustrasjon av Logic NOT Gate:

La oss anta at 'A' er inngangen og 'Y' er utgangen, den boolske ligningen for logikk IKKE gate er: Ā = Y.

Ligningen sier at utgangen er inversjon av inngangen.

Sannhetstabell for logikk IKKE gate:

| TIL (INNGANG) | Y (PRODUKSJON) |

| 0 | 1 |

| 1 | 0 |

De ikke portene vil alltid ha en enkelt inngang (og alltid ha en enkelt utgang) den er kategorisert som beslutningsenheter. “O” -symbolet på toppen av trekanten representerer komplementering eller inversjon.

Dette 'o' -symbolet er ikke bare begrenset til den logiske 'IKKE' -porten, men kan også brukes av alle logiske porter eller en hvilken som helst digital krets. Hvis “o” er ved inngangen, angir dette at inngangen er aktiv-lav.

Aktiv-lav: Utgangen blir aktiv (aktivering av en transistor, en LED eller et relé osv.) Når “LAV” inngang er gitt.

NAND og NOR Gates Equivalent:

'IKKE' -porten kan konstrueres ved hjelp av logiske 'NAND' og logiske 'NOR' porter ved å koble sammen alle inngangspinnene, dette gjelder porter med 3, 4 og høyere inngangspinner.

Transistorbasert logikk “IKKE” gate:

Logikken 'NOT' kan konstrueres av en NPN-transistor og en 1K-motstand. Hvis vi bruker 'HIGH' -signal på basen til transistoren, blir bakken koblet til transistorens kollektor, og dermed blir utgangen 'LAV'.

Hvis vi bruker 'LAV' -signal til bunnen av transistoren, forblir transistoren AV og vil ikke være koblet til bakken, men utgangen vil bli trukket 'HØY' av opptrekksmotstanden som er koblet til Vcc. Dermed kan vi lage en logisk 'IKKE' gate ved hjelp av transistor.

Schmitt-omformere:

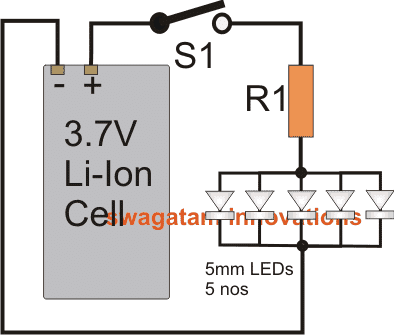

Vi vil utforske dette konseptet med en automatisk batterilader for å forklare bruken og funksjonen til Schmitt-omformerne. La oss ta eksemplet på prosedyre for lading av litiumionbatterier.

3,7 V li-ion-batteriet lades når batteriet treffer 3 V til 3,2 V, batterispenningen stiger gradvis under lading, og batteriet må kuttes ved 4,2 V. Etter lading faller batteriets åpne kretsspenning rundt 4,0 V .

En spenningssensor måler grenseverdien og utløser reléet for å stoppe lading. Men når spenningen synker under 4,2 V, oppdager laderen at den ikke er ladet og begynner ladingen til 4,2 V og avbrytelse, igjen faller batterispenningen til 4,0 V og begynner ladingen igjen, og denne galskapen går igjen og igjen.

Dette vil drepe batteriet raskt. For å løse dette problemet trenger vi et lavere terskelnivå eller 'LTV' slik at batteriet ikke starter å lade opp før batteriet faller til 3 V til 3,2 V. Den øvre terskelspenningen eller 'UTV' er 4.2V i dette eksemplet.

En Schmitt-inverter er laget for å bytte utgangstilstand når spenningen krysser den øvre terskelspenningen og den forblir den samme til inngangen når den nedre terskelspenningen.

Når inngangen er krysset lavere terskelspenning, forblir utgangen den samme til inngangen når den øvre terskelspenningen.

Det vil ikke endre tilstanden mellom LTV og UTV.

Nå, på grunn av dette, vil ON / OFF være mye jevnere og uønsket svingning vil bli fjernet, og også kretsen vil være mer motstandsdyktig mot elektrisk støy.

Schmitt IKKE portoscillator:

Ovennevnte krets er en oscillator som produserer firkantbølge ved 33% driftssyklus. Opprinnelig er kondensatoren i utladet tilstand, og bakkesignalet vil være tilgjengelig ved inngangen til IKKE porten.

Utgangen blir positiv og lader kondensatoren via motstanden 'R', kondensatoren lades til den øvre terskelspenningen til omformeren og endrer tilstanden, utgangen blir negativt signal og kondensatoren begynner å utlades via motstanden 'R' til kondensatorspenningen når det lavere terskelnivået og endrer tilstanden, blir utgangen positiv og lader kondensatoren.

Denne syklusen gjentas så lenge strømforsyningen blir gitt til kretsen.

Frekvensen til oscillatoren ovenfor kan beregnes: F = 680 / RC

Hvor, F er frekvens.

R er motstand i ohm.

C er kapasitans i farad.

Firkantbølgekonverterer:

Ovennevnte krets vil konvertere sinusbølgesignal til firkantbølge, faktisk kan den konvertere alle analoge bølger til firkantbølge.

De to motstandene R1 og R2 fungerer som spenningsdeler, dette brukes til å få et forspenningspunkt og kondensatoren blokkerer eventuelle DC-signaler.

Hvis inngangssignalet går over øvre terskelnivå eller under nedre terskelnivå, blir utgangen

LAV eller HØY i henhold til signalet, produserer dette firkantbølge.

IC 7404 IKKE gateomformer:

IC 7404 er en av de mest brukte logikk IKKE gate IC. Den har 14 pinner, pin # 7 er malt og pin nr. 14 er Vcc. Driftsspenningen er fra 4,5V til 5V.

Forplantningsforsinkelse:

Forplantningsforsinkelsen er tiden det tar av porten å behandle utgangen etter å ha gitt en inngang.

I logikk tar det '22 IKKE' gate rundt 22 nano sekunder å endre tilstanden fra HØY til LAV og omvendt.

Det er flere andre logiske 'IKKE gate ICer:

• 74LS04 Hex Inverterende IKKE port

• 74LS14 Hex Schmitt inverterende IKKE port

• 74LS1004 Hex-inverterende drivere

• CD4009 Hex Inverting NOT Gate

• CD4069 Hex Inverting NOT Gate

Hvordan ELLER gate fungerer

La oss nå utforske om digital logikk ELLER porter. Vi vil ta en titt på den grunnleggende definisjonen, symbolet, sannhetstabellen, Multi input ELLER gate, vi skal konstruere transistorbasert 2 inngang ELLER gate og til slutt vil vi ta en oversikt over OR gate IC 7432.

Hva er Logic “OR” Gate?

Det er en elektronisk port, hvis utgang blir 'LAV' eller '0' eller 'falsk' eller gir ut et 'negativt signal' når alle inngangene til ELLER-portene er 'LAV' eller '0' eller 'falsk' eller ' negativt signal ”.

For eksempel: Si en ELLER-port med ‘n’ antall innganger, hvis alle inngangene er “LAV” blir utgangen “LAV”. Selv om en inngang er “HIGH” eller “1” eller “true” eller “positive signal”, blir utgangen “HIGH” eller “1” eller “true” eller gir et “positivt signal”.

Merk:

Uttrykket “Høy”, “1”, “positivt signal”, “sant” er egentlig det samme (Positivt signal er batteriets eller strømforsyningens positive signal).

Begrepet 'LAV', '0', 'negativt signal', 'falsk' er i det vesentlige det samme (negativt signal er batteriets eller strømforsyningens negative signal).

Illustrasjon av logikk ELLER port symbol:

Her er 'A' og 'B' de to inngangene, og 'Y' blir sendt ut.

Det boolske uttrykket for logikk ELLER gate: Utgangen 'Y' er tillegg av de to inngangene 'A' og 'B', (A + B) = Y.

Det boolske tillegget er betegnet med (+)

Hvis ‘A’ er ‘1’ og ‘B’ er ‘1’ er utgangen (A + B) = 1 + 1 = ‘1’ eller “høy”

Hvis 'A' er '0' og 'B' er '1' er utgangen (A + B) = 0 + 1 = '1' eller 'høy'

Hvis 'A' er '1' og 'B' er '0' er utgangen (A + B) = 1 + 0 = '1' eller 'høy'

Hvis ‘A’ er ‘0’ og ‘B’ er ‘0’ er utgangen (A + B) = 0 + 0 = ‘0’ eller “Lav”

Ovennevnte forhold er forenklet i sannhetstabellen.

Sannhetstabell (to innganger):

| A (inngang) | B (INNGANG) | Y (utgang) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

3-inngangs 'ELLER' -port:

Illustrasjon av 3 inngang ELLER port:

Logiske ELLER-porter kan ha ‘n’ antall innganger, noe som betyr at det kan ha mer enn to innganger (Logiske ELLER-porter vil ha minst to innganger og alltid en utgang).

For en 3-inngangslogikk ELLER-gate blir den boolske ligningen slik: (A + B + C) = Y, på samme måte for 4 innganger og over.

Sannhetstabell for 3 inngangslogikk ELLER gate:

| A (INNGANG) | B (INNGANG) | C (INNGANG) | Y (UTGANG) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Multi-inngangslogikk ELLER porter:

Kommersielt tilgjengelige logiske ELLER porter er bare tilgjengelige i 2, 3 og 4 innganger. Hvis vi har mer enn 4 innspill, må vi kaskade portene.

Vi kan ha seks inngangslogikk ELLER gate ved å kaskade de 2 inngang ELLER portene som følger:

Nå blir den boolske ligningen for kretsen ovenfor Y = (A + B) + (C + D) + (E + F)

Likevel gjelder alle de nevnte logiske reglene for kretsen ovenfor.

Hvis du bare vil bruke 5 innganger fra de ovennevnte 6 inngangene ELLER porten, kan vi koble en nedtrekkbar motstand på en hvilken som helst pin, og nå blir det 5 inngang ELLER port.

Transistorbasert to-inngangs logisk ELLER gate:

Nå vet vi hvordan en logikk ELLER gate fungerer, la oss konstruere en 2 inngang ELLER gate ved hjelp av to NPN-transistorer. De logiske IC-ene er konstruert på nesten samme måte.

To skjema for transistor ELLER port:

Ved utgangen “Y” kan du koble til en LED hvis utgangen er høy, vil LED-en lyse (LED + Ve-terminal på “Y” med 330 ohm motstand og negativ til GND).

Når vi bruker LAVT signal til basen til de to transistorene, slås begge transistorene AV, bakkesignalet vil være tilgjengelig på emitteren til T2 / T1 via 1k nedtrekksmotstand, og dermed blir utgangen LAV.

Hvis en av transistoren er PÅ, vil positiv spenning være tilgjengelig på senderen av T2 / T1, og dermed blir utgangen HØY.

Nå vet du hvordan du lager din egen logikk ELLER gate.

Quad ELLER gate IC 7432:

Hvis du vil kjøpe logikk ELLER gate fra markedet, vil du komme i konfigurasjonen ovenfor.

Den har 14 pinner, pin nr. 7 og pin nr. 14 er henholdsvis GND og Vcc. Den drives på 5V.

Forplantningsforsinkelse:

Forplantningsforsinkelse er tiden det tar for produksjonen å endre seg fra LAV til HØY og omvendt.

Forplantningsforsinkelsen fra LAV til HØY er 7,4 nanosekunder ved 25 grader Celsius.

Forplantningsforsinkelsen fra HIGH til LOW er 7,7 nanosekunder ved 25 grader Celsius.

• 74LS32 Quad 2-inngang

• CD4071 Quad 2-inngang

• CD4075 Triple 3-inngang

• CD4072 Dual 4-inngang

Logikk eksklusiv –eller port

I dette innlegget skal vi utforske om logikk XOR gate eller Exclusive-OR gate. Vi vil ta en titt på den grunnleggende definisjonen, symbolet, sannhetstabellen, XOR-ekvivalent krets, XOR-realisering ved hjelp av logiske NAND-porter, og til slutt vil vi ta oversikt over quad 2-inngang Ex-OR gate IC 7486.

I de forrige innleggene lærte vi om tre grunnleggende logiske porter “OG”, “ELLER” og “IKKE”. Vi lærte også at ved å bruke disse tre grunnleggende portene kan vi konstruere to nye logiske porter 'NAND' og 'NOR'.

Det er to flere logiske porter, selv om disse to ikke er grunnleggende porter, men den er konstruert av kombinasjonen av de andre logiske portene, og dens boolske ligning er så viktig og veldig nyttig at den anses som forskjellige logiske porter.

Disse to logiske portene er “Exclusive OR” gate og “Exclusive NOR”. I dette innlegget skal vi bare utforske om logikk Eksklusiv ELLER gate.

Hva er 'Exclusive OR' gate?

Det er en elektronisk port, hvis utgang blir 'høy' eller '1' eller 'sann' eller gir et 'positivt signal' når de to logiske inngangene er forskjellige i forhold til hverandre (dette gjelder bare for to 2-inngangseks. -ELLER port).

For eksempel: Si en eksklusiv ELLER-gate med 'to' innganger, hvis en av inngangsstiftene A er 'HØY' og inngangsstiften B er 'LAV', blir utgangen 'HØY' eller '1' eller 'sann' eller “Positivt signal”.

Hvis begge inngangene har samme logiske nivå, dvs. begge pinnene “HIGH” eller begge pinnene “LOW” blir utgangen “LOW” eller “0” eller “false” eller “negative signal”.

Merk:

Uttrykket “Høy”, “1”, “positivt signal”, “sant” er egentlig det samme (Positivt signal er batteriets eller strømforsyningens positive signal).

Begrepet 'LAV', '0', 'negativt signal', 'falsk' er i det vesentlige det samme (negativt signal er batteriets eller strømforsyningens negative signal).

Illustrasjon av Logic Exclusive ELLER gate:

Her er 'A' og 'B' de to inngangene, og 'Y' blir sendt ut.

Det boolske uttrykket for logikk Ex-OR gate: Y = (A.) ̅B + A.B ̅

Hvis ‘A’ er ‘1’ og ‘B’ er ‘1’ er utgangen (A ̅.B + A.B ̅) = 0 x 1 + 1 x 0 = ‘1’ eller “LAV”

Hvis ‘A’ er ‘0’ og ‘B’ er ‘1’ er utgangen (A ̅.B + A.B ̅) = 1 x 1 + 0 x 0 = ‘1’ eller ‘HØY’

Hvis ‘A’ er ‘1’ og ‘B’ er ‘0’ er utgangen (A ̅.B + A.B ̅) = 0 x 0 + 1 x 1 = ‘1’ eller “HØY”

Hvis ‘A’ er ‘0’ og ‘B’ er ‘0’ er utgangen (A ̅.B + A.B ̅) = 1 x 0 + 0 x 1 = ‘0’ eller “Lav”

Ovennevnte forhold er forenklet i sannhetstabellen.

Sannhetstabell (to innganger):

| A (inngang) | B (INNGANG) | Y (utgang) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

I de to ovennevnte logiske Ex-OR-portene, hvis de to inngangene er forskjellige, dvs. “1” og “0” blir utgangen “HIGH”. Men med 3 eller flere inngangslogikk Ex-OR eller generelt blir Ex-ORs utgang 'HIGH' bare når ODD-nummeret til logikk 'HIGH' blir brukt på porten.

For eksempel: Hvis vi har 3 inngangs-EX-ELLER-gate, hvis vi bruker logikk “HIGH” på bare én inngang (oddetall logikk “1”) blir utgangen “HIGH”. Hvis vi bruker logikk “HIGH” på to innganger (dette er jevnt antall logiske “1”) blir utgangen “LAV” og så videre.

3 innganger eksklusiv ELLER port:

Illustrasjon av 3 inngangs EX-ELLER-port:

Sannhetstabell for 3 inngangslogikk EX-OR-gate:

| A (INNGANG) | B (INNGANG) | C (INNGANG) | Y (UTGANG) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

For Ex-OR-porten med 3 innganger blir den boolske ligningen: A (BC) ̅ + A ̅BC ̅ + (AB) ̅C + ABC

Som vi beskrev tidligere, er ikke den logiske 'Ex-OR' -porten en grunnleggende logikkport, men en kombinasjon av forskjellige logiske porter. Ex-OR-porten kan realiseres ved hjelp av logisk 'ELLER' -port, logisk 'OG' -port og logisk 'NAND' -port som følger:

Tilsvarende krets for “Exclusive OR” gate:

Ovennevnte design har stor ulempe, vi trenger 3 forskjellige logiske porter for å lage en Ex-OR-port. Men vi kan overvinne dette problemet ved å implementere Ex-OR gate med bare logiske NAND-porter, dette er også økonomisk å lage.

Eksklusiv ELLER gate ved hjelp av NAND gate:

Eksklusive ELLER-porter brukes til å utføre kompliserte databehandlingsoppgaver som aritmetiske operasjoner, fulladdere, halvaddere, det kan også levere utføringsfunksjonalitet.

Logikk Eksklusiv ELLER Gate IC 7486:

Hvis du vil kjøpe logisk Ex-OR gate fra markedet, vil du komme i DIP-konfigurasjonen ovenfor.

Den har 14 pinner, pin nr. 7 og pin nr. 14 er henholdsvis GND og Vcc. Den drives på 5V.

Forplantningsforsinkelse:

Forplantningsforsinkelse er tiden det tar for utgangen å endre seg fra LAV til HØY og omvendt etter å ha gitt innspill.

Forplantningsforsinkelsen fra LAV til HØY er 23 nanosekunder.

Forplantningsforsinkelsen fra HØY til LAV er 17 nanosekunder.

Vanlig tilgjengelige “EX-OR” gate ICer:

- 74LS86 Quad 2-inngang

- CD4030 Quad 2-inngang

Jeg håper ovennevnte detaljerte forklaring kan ha hjulpet deg til å forstå hva logiske porter er og hvordan logiske porter fungerer, hvis du fortsatt har spørsmål? Vennligst uttrykk i kommentarseksjonen, du kan få et raskt svar.

Forrige: Kondensatorlekkasje-testerkrets - Finn raskt lekke kondensatorer Neste: Digital Buffer - Working, Definition, Truth Table, Double Inversion, Fan-out

![IC 4060 låseproblem [løst]](https://electronics.jf-parede.pt/img/timer-delay-relay/35/ic-4060-latching-problem.jpg)