Denne artikkelen forklarer generering av pulsbreddemodulasjon signaler med variabel driftssyklus på FPGA ved bruk av VHDL. PWM har en fast frekvens og en variabel spenning. Denne artikkelen diskuterer også Digital Clock Manager for å redusere klokkefrekvensen ved å redusere skjevheten til kloksignalet. En fast frekvens brukes til å produsere inngangsdataene som produserer PWM-signalene ved hjelp av en komparator. Elektroniske selskaper designer maskinvaren dedikert til produktene sine med sine standarder og protokoller, noe som gjør det utfordrende for sluttbrukerne å konfigurere maskinvaren etter deres behov. Dette kravet til maskinvare førte til veksten av et nytt segment av kundekonfigurerbart feltprogrammerbare integrerte kretser kalt FPGAer .

Pulsbreddemodulering (PWM)

Pulsbreddemodulering er mye brukt i applikasjoner for kommunikasjon og kontrollsystemer . Pulsbreddemodulering kan genereres ved hjelp av forskjellige tilnærminger i kontrollsystemer. Her, i denne artikkelen, blir PWM generert ved hjelp av Hardware Description Language (VHDL) og implementert på FPGA. Implementering av PWM på FPGA kan behandle data raskere og kontrollerarkitektur kan optimaliseres for plass eller hastighet.

PWM er en teknikk for å gi logikk '0' og logikk '1' i en kontrollert tidsperiode. Det er en signalkilde som involverer modulering av driftssyklusen for å kontrollere mengden kraft som sendes til lasten. I PWM holdes tidsperioden for firkantbølgen konstant, og tiden som signalet forblir HØY varieres.

PWM genererer pulser på utgangen på en slik måte at gjennomsnittsverdien for HIGHs og LOWs er proporsjonal med PWM-inngangen. Driftssyklusen til signalet kan varieres. Et PWM-signal er en konstant periodebølge med varierende driftssyklus. Det vil si at frekvensen til PWM-signalet er konstant, men tidsperioden til signalet forblir høy og varierer som vist.

PWM-signal

VHDL

VHDL er et språk som brukes til å beskrive atferden til design av digitale kretser . VHDL brukes av bransjer og akademikere med det formål å simulere digitale kretser. Dens design kan simuleres og oversettes i form som er egnet for implementering i maskinvare.

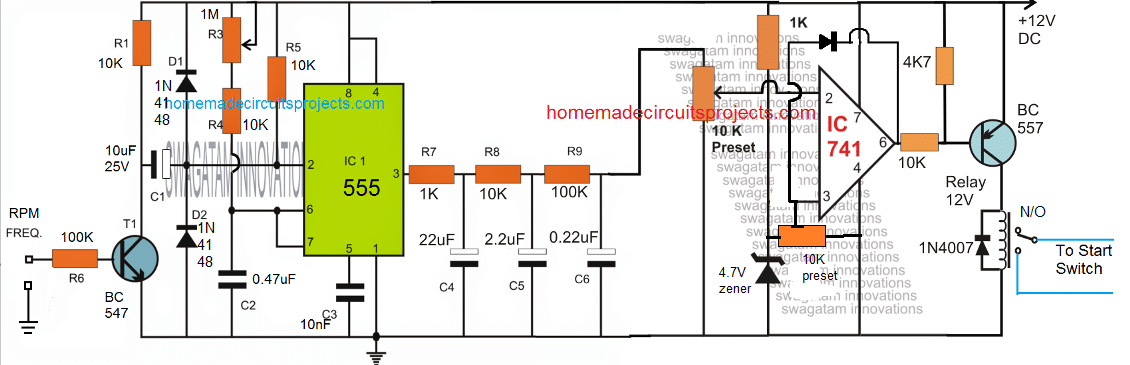

PWM-arkitektur

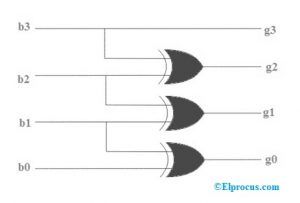

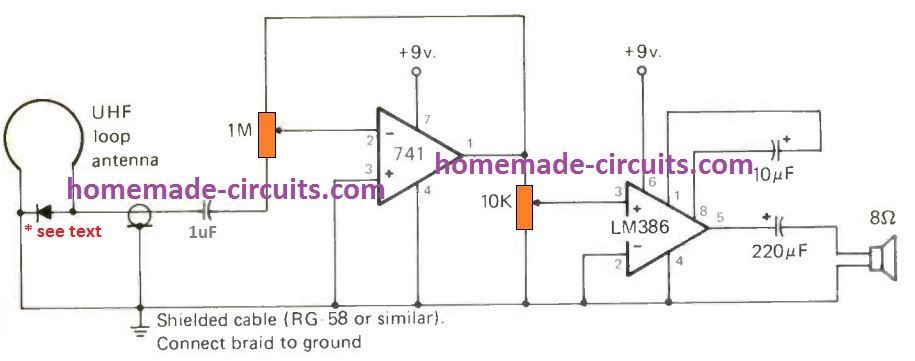

Å produsere inngangsdataene for å generere PWM ved hjelp av en høyhastighets N-bit gratis løpsteller, hvis utgang blir sammenlignet med registerutgang og lagrer ønsket inngangssyklus ved hjelp av komparator. Sammenligningen utgangen er satt til 1 når begge disse verdiene er like. Denne komparatorutgangen brukes til å stille inn RS-låsen. Overløpssignalet fra telleren brukes til å tilbakestille RS-låsen. De utgang fra RS-låsen gir ønsket PWM-utgang. Dette overløpssignalet brukes også til å laste ny N-bit driftssyklus i registeret. PWM har en fast frekvens og en variabel spenning. Denne spenningsverdien endres fra 0V til 5 V.

PWM-signal med variabel driftssyklus

Den grunnleggende PWM genererer signalene, som gir utgang fra PWM, krever en komparator som sammenligner mellom to verdier. Den første verdien representerer kvadrat signalet generert av N bit telleren og den andre verdien representerer kvadrat signalet som inneholder informasjonen om driftssyklus. Telleren genererer belastningssignalet når det er overløp. Når belastningssignalet blir aktivt, laster registeret inn den nye driftssyklusverdien. Lastsignalet brukes til å tilbakestille låsen også. Låseutgang er et PWM-signal. Dette varierer med endringen i driftssyklusverdien.

Hva er FPGA?

FPGA er feltprogrammerbar gate matrise. Det er en type enhet som er mye brukt i elektroniske kretser. FPGA er halvlederinnretninger som inneholder programmerbare logiske blokker og samtrafikkretser. Den kan programmeres eller omprogrammeres til ønsket funksjonalitet etter produksjon.

FPGA

Grunnleggende om FPGA

Når et kretskort er produsert, og hvis det inneholder en FPGA som en del av det. Dette er programmert under produksjonsprosessen, og videre kan omprogrammeres senere for å lage en oppdatering eller gjøre nødvendige endringer. Denne funksjonen i FPGA gjør den unik fra ASIC. Applikasjonsspesifikke integrerte kretser (ASIC) er skreddersydd for spesifikke designoppgaver. Tidligere ble FPGA-er brukt til å utvikle lav hastighet, kompleksitet og volumdesign, men i dag vil FPGA enkelt skyve ytelsesbarrieren opp til 500 MHz.

I mikrokontrollere er brikken designet for en kunde, og de må skrive programvaren og kompilere den til hex-fil for å lastes på mikrokontrolleren. Denne programvaren kan enkelt byttes ut fordi den er lagret i flashminnet. I FPGA-er er det ingen prosessor som kjører programvaren, og det er vi som designer kretsen. Vi kan konfigurere en FPGA så enkel som en AND-gate eller en kompleks som en flerkjerneprosessor. For å lage et design skriver vi Hardware Description Language (HDL), som er av to typer - Verilog og VHDL. Deretter syntetiseres HDL til en bitfil ved hjelp av en BITGEN for å konfigurere FPGA. FPGA lagrer konfigurasjonen i RAM, det vil si at konfigurasjonen går tapt når det ikke er strømtilkobling. Derfor må de konfigureres hver gang strøm leveres.

Arkitektur av FPGA

FPGA er prefabrikkerte silisiumchips som kan programmeres elektrisk for å implementere digital design. Den første statiske minnebaserte FPGA kalt SRAM brukes til å konfigurere både logikk og samtrafikk ved hjelp av en strøm av konfigurasjonsbiter. Dagens moderne EPGA inneholder omtrent 3 30 000 logiske blokker og rundt 1100 innganger og utganger.

FPGA Arkitektur

Arkitekturen til FPGA består av tre hovedkomponenter

- Programmerbare logiske blokker, som implementerer logiske funksjoner

- Programmerbar ruting (samtrafikk), som implementerer funksjoner

- I / O-blokker, som brukes til å lage tilkoblinger utenfor brikken

Anvendelser av PWM-signaler

PWM-signaler brukes mye for kontrollapplikasjoner. Som å kontrollere likestrømsmotorer, reguleringsventiler, pumper, hydraulikk, etc. Her er de få anvendelsene av PWM-signalene.

- Varmesystemer med langsom tid 10 til 100Hz eller høyere.

- DC-elektriske motorer 5 til 10 KHz

- Strømforsyninger eller lydforsterkere 20 til 200 KHz.

Denne artikkelen handler om generering av PWM-signaler med variabel driftssyklus ved bruk av FPGA. Videre, for all hjelp til elektroniske prosjekter eller tvil angående denne artikkelen, kan du kontakte oss ved å kommentere kommentarseksjonen gitt nedenfor.