Ulike typer digitale systemer er konstruert fra svært få typer grunnleggende nettverkskonfigurasjoner som AND gate, NAND gate, Eller gate, etc ... Disse elementære kretsene brukes om og om igjen i forskjellige topologiske kombinasjoner. I tillegg til å utføre logikk, må digitale systemer også lagre binære tall. For disse minnecellene, også kjent som FLIP-FLOP ’ s er designet. For å utføre noen funksjoner som binær tillegg. Derfor å utføre slike funksjoner, kombinasjoner av logiske porter og FLIP-FLOP er designet over en enkeltbrikke IC. Disse IC-ene danner de praktiske byggesteinene til de digitale systemene. En av slike byggesteiner som brukes til binær tillegg er Carry Look-ahead Adder.

Hva er en Carry Look-ahead Adder?

En digital datamaskin må inneholde kretser som kan utføre aritmetiske operasjoner som addisjon, subtraksjon, multiplikasjon og divisjon. Blant disse er addisjon og subtraksjon de grunnleggende operasjonene mens multiplikasjon og divisjon er henholdsvis gjentatt addisjon og subtraksjon.

For å utføre disse operasjonene implementeres 'Adder-kretser' ved hjelp av grunnleggende logiske porter. Adder kretser utvikles som Half-adder, Full-adder, Ripple-carry Adder og Carry Look-ahead Adder.

Blant disse Carry Look-ahead Adder er den raskere adderkretsen. Det reduserer forplantningsforsinkelsen, som oppstår under tilsetning, ved å bruke mer komplekse maskinvarekretser. Den er designet ved å transformere ringbære-Adder-kretsen slik at bærelogikken til huggeren endres til to-nivå logikk.

4-biters Carry Look-ahead Adder

I parallelle addere blir bæreoutputtet til hver fulladder gitt som en bæreinngang til neste høyere ordens tilstand. Derfor er det ikke mulig å produsere bære- og sumoutput fra noen tilstand med mindre det er en bæreinngang tilgjengelig for den tilstanden.

Så for at beregning skal skje, må kretsen vente til bærebiten forplantes til alle stater. Dette induserer bæreutbredelsesforsinkelse i kretsen.

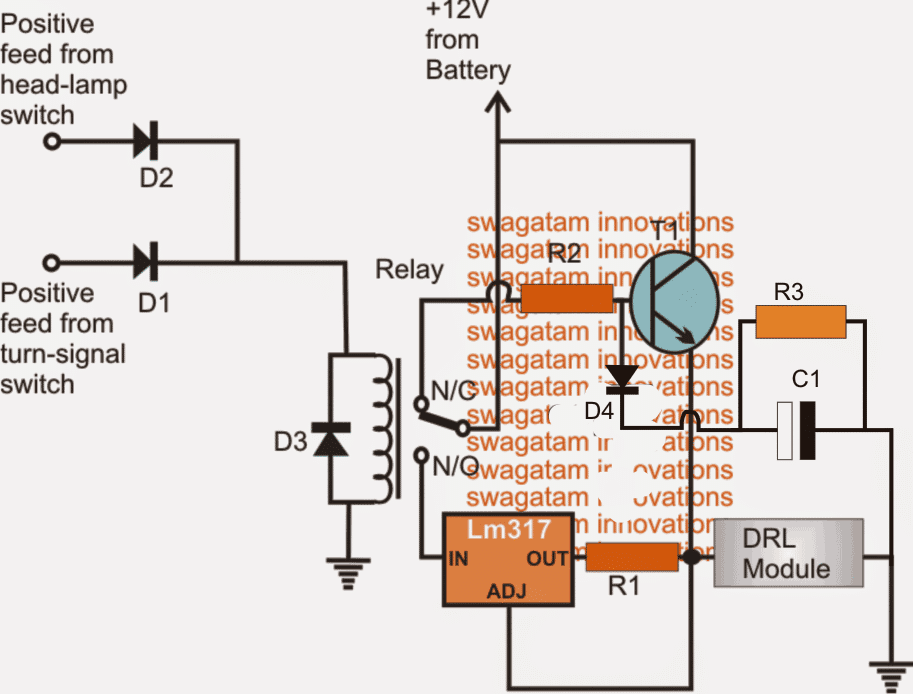

4-bit-Ripple-Carry-Adder

Tenk på 4-bit krusningsbærehodekretsen ovenfor. Her kan summen S3 produseres så snart inngangene A3 og B3 er gitt. Men bære C3 kan ikke beregnes før bærebiten C2 påføres mens C2 er avhengig av C1. Derfor, for å produsere endelige resultater i steady-state, må bæring forplante seg gjennom alle statene. Dette øker forsinkelsen for bæreutbredelse av kretsen.

Fortplantningsforsinkelsen til addereren beregnes som 'forplantningsforsinkelsen for hver gate ganger antall trinn i kretsen'. For beregning av et stort antall biter, må flere trinn legges til, noe som gjør forsinkelsen mye verre. Derfor, for å løse denne situasjonen, ble Carry Look-ahead Adder introdusert.

For å forstå funksjonen til en Carry Look-ahead Adder, er en 4-bit Carry Look-ahead Adder beskrevet nedenfor.

4-bit-Carry-Look-ahead-Adder-Logic-Diagram

I denne adderen er bæreinngangen på hvilket som helst trinn i adderen uavhengig av bærebittene som genereres i de uavhengige stadiene. Her er utgangen fra et hvilket som helst trinn bare avhengig av bitene som er lagt til i de forrige trinnene og bæreinngangen som ble gitt i begynnelsen. Derfor trenger ikke kretsen på hvilket som helst trinn å vente på generering av bærebit fra forrige trinn, og bærebit kan evalueres når som helst.

Truth Table of Carry Look-ahead Adder

For å utlede sannhetstabellen til denne adderen, introduseres to nye begreper - Carry generere og bære propagate. Carry generer Gi = 1 når det genereres en bærer Ci + 1. Det avhenger av Ai og Bi-innganger. Gi er 1 når både Ai og Bi er 1. Derfor beregnes Gi som Gi = Ai. Bi.

Bæreforplantet Pi er assosiert med forplantning av bære fra Ci til Ci + 1. Det beregnes som Pi = Ai ⊕ Bi. Sannhetstabellen til denne adderen kan avledes av å endre sannhetstabellen til en fulladder.

Ved å bruke Gi og Pi-uttrykkene er Sum Si og Carry Ci + 1 gitt som nedenfor -

- Si = Pi ⊕ Gi.

- Ci + 1 = Ci.Pi + Gi.

Derfor kan bærebitene C1, C2, C3 og C4 beregnes som

- C1 = C0.P0 + G0.

- C2 = C1.P1 + G1 = (C0.P0 + G0). P1 + G1.

- C3 = C2.P2 + G2 = (C1.P1 + G1). P2 + G2.

- C4 = C3.P3 + G3 = C0.P0.P1.P2.P3 + P3.P2.P1.G0 + P3.P2.G1 + G2.P3 + G3.

Det kan observeres fra ligningene som bærer Ci + 1, avhenger bare av bæringen C0, ikke av de mellomliggende bærebitene.

Carry-Look-ahead-Adder-Truth-Table

Kretsdiagram

Ovennevnte ligninger er implementert ved hjelp av to-nivå kombinasjonskretser sammen med AND, ELLER porter, der porter antas å ha flere innganger.

Carry-Output-Generation-Circuit-of-Carry-Look-ahead-Adder

Carry Look-ahead Adder-kretsen fra 4-bit er gitt nedenfor.

4-bit-Carry-Look-ahead-Adder-Circuit-Diagram

8-biters og 16-biters Carry Look-ahead Adder-kretser kan utformes ved å kaste 4-biters adderkrets med bærelogikk.

Fordeler med Carry Look-ahead Adder

I denne adderen reduseres forplantningsforsinkelsen. Bæreutgangen på et hvilket som helst trinn er bare avhengig av den innledende bærebiten til begynnelsesfasen. Ved hjelp av denne adderen er det mulig å beregne mellomresultatene. Denne huggeren er den raskeste huggeren som brukes til beregning.

applikasjoner

High-speed Carry Look-ahead Adders brukes som implementert som IC-er. Derfor er det lett å legge inn huggeren i kretsløp. Ved å kombinere to eller flere addere kan beregninger av høyere boolske funksjoner gjøres enkelt. Her er økningen i antall porter også moderat når den brukes til høyere biter.

For denne Adder er det en avveining mellom område og hastighet. Når det brukes til høyere bitberegninger, gir det høy hastighet, men kompleksiteten til kretsen økes, og øker dermed området opptatt av kretsen. Denne adderen implementeres vanligvis som 4-bits moduler som kaskades sammen når de brukes til høyere beregninger. Denne adderen er dyrere sammenlignet med andre addere.

For boolsk beregning på datamaskiner brukes addere regelmessig. Charles Babbage implementerte en mekanisme for å forutse bærebiten i datamaskiner, for å redusere forsinkelsen forårsaket av krusningsbærere . Mens du designer et system, er beregningshastigheten den høyeste avgjørende faktoren for en designer. I 1957 patenterte Gerald B. Rosenberger den moderne Binary Carry Look-ahead Adder. Basert på analysen av portforsinkelse og simulering, blir det utført eksperimenter for å modifisere kretsen til denne huggeren for å gjøre den enda raskere. For en n-bit bærer blikk fremover, hva er forplantningsforsinkelsen når en forsinkelse for hver port er 20?

Bildekreditt